41-52 Vol. 3D

SGX INSTRUCTION REFERENCES

EPA—Add Version Array

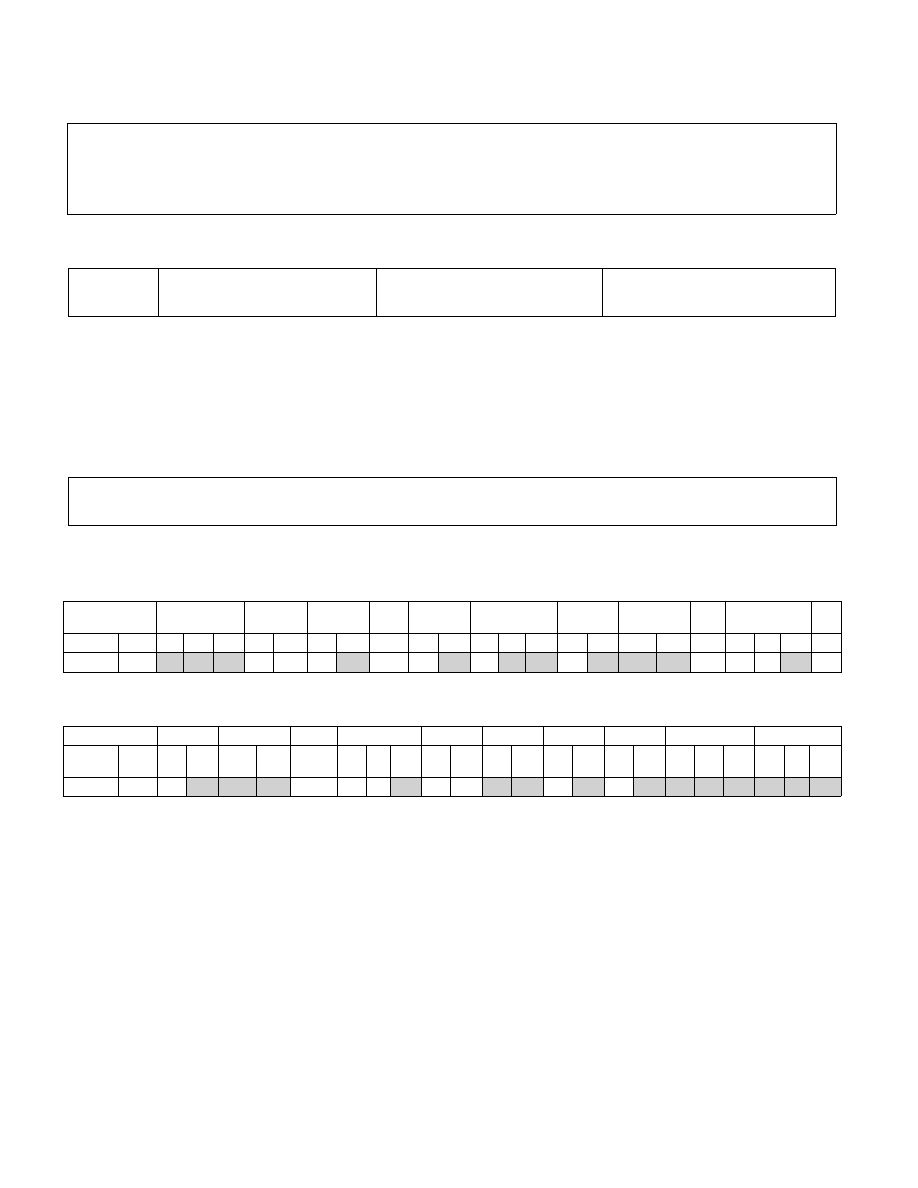

Instruction Operand Encoding

Description

This leaf function

creates an empty version array in the EPC page whose logical address is given by DS:RCX, and

sets up EPCM attributes for that page. At the time of execution of this instruction, the register RBX must be set to

PT_VA.

The table below provides additional information on the memory parameter of EPA leaf function.

EPA Memory Parameter Semantics

Concurrency Restrictions

Operation

IF (RBX ≠ PT_VA or DS:RCX is not 4KByte Aligned)

THEN #GP(0); FI;

IF (DS:RCX does not resolve within an EPC)

THEN #PF(DS:RCX); FI;

(* Check concurrency with other Intel SGX instructions *)

IF (Other Intel SGX instructions accessing the page)

THEN #GP(0); FI;

Opcode/

Instruction

Op/En

64/32

bit Mode

Support

CPUID

Feature

Flag

Description

EAX = 0AH

IR

V/V

SGX1

This leaf function adds a Version Array to the EPC.

ENCLS[EPA]

Op/En

EAX

RBX

RCX

IR

EPA (In)

PT_VA (In, Constant)

Effective address of the EPC page (In)

EPCPAGE

Write access permitted by Enclave

Table 41-34. Concurrency Restrictions of EPA with Other Intel® SGX Operations 1 of 2

Operation

EEXIT

EADD

EBLOCK

ECRE

ATE

EDBGRD/

WR

EENTER/

ERESUME

EEXTEND

EGETKEY

EINIT

ELDB/ELDU

EPA

Param TCS SSA SECS Targ SECS Targ SECS SECS

Targ SECS TCS SSA SECS Targ SECS Param SECS SECS Targ VA

SECS VA

EPA

VA

N

N

N

N

N

N

N

N

N

N

N

Table 41-35. Concurrency Restrictions of EPA with Other Intel® SGX Operations 2 of 2

Operation

EREMOVE

EREPORT

ETRACK

EWB

EAUG

EMODPE

EMODPR

EMODT

EACCEPT

EACCEPTCOPY

Param Targ SECS Param SECS SECS

SRC VA SECS Targ SECS Targ SECI

NFO

Targ SECS Targ SECS Targ SECI

NFO

SECS Targ SR

C

SECI

NFO

EPA

VA

N

N

N

N

N

N

N

N