41-50 Vol. 3D

SGX INSTRUCTION REFERENCES

Operation

Temp Variables in EMODT Operational Flow

IF (DS:RBX is not 64Byte Aligned)

THEN #GP(0); FI;

IF (DS:RCX is not 4KByte Aligned)

THEN #GP(0); FI;

IF (DS:RCX does not resolve within an EPC)

THEN #PF(DS:RCX); FI;

SCRATCH_SECINFO DS:RBX;

(* Check for mis-configured SECINFO flags*)

IF ( (SCRATCH_SECINFO reserved fields are not zero ) or

!(SCRATCH_SECINFO.FLAGS.PT is PT_TCS or SCRATCH_SECINFO.FLAGS.PT is PT_TRIM) )

THEN #GP(0); FI;

(* Check concurrency with SGX1 instructions on the EPC page *)

IF (other SGX1 instructions accessing EPC page)

THEN #GP(0); FI;

IF (EPCM(DS:RCX).VALID is 0 or

!(EPCM(DS:RCX).PT is PT_REG or EPCM(DS:RCX).PT is PT_TCS))

THEN #PF(DS:RCX); FI;

(* Check the EPC page for concurrency *)

IF (EPC page in use by another SGX2 instruction)

THEN #GP(0); FI;

(* Check for mis-configured SECINFO flags*)

IF ( (EPCM(DS:RCX).R = 0) and (SCRATCH_SECINFO.FLAGS.R = 0) and (SCRATCH_SECINFO.FLAGS.W ≠ 0) ))

THEN

RFLAGS 1;

RAX SGX_LOCKFAIL;

GOTO DONE;

FI;

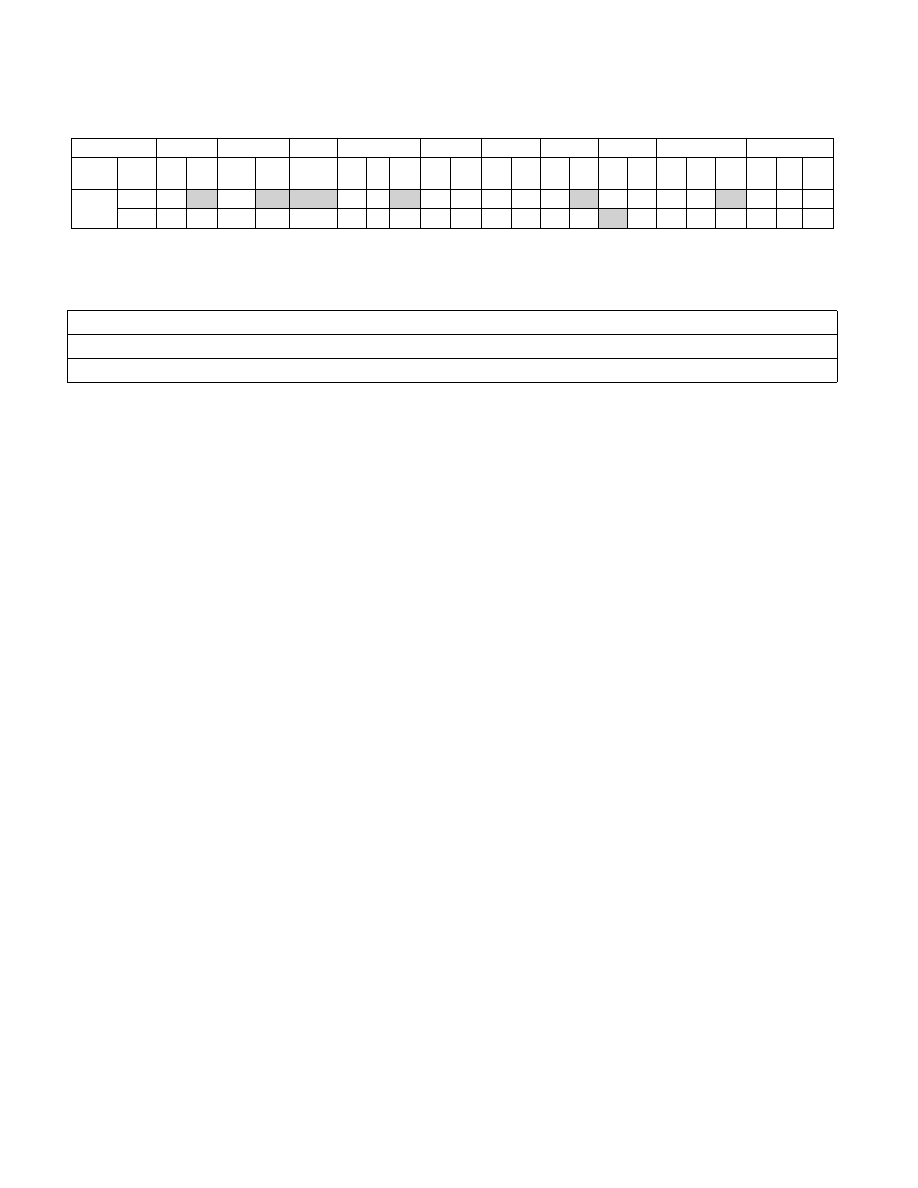

Table 41-33. Concurrency Restrictions of EMODT with Other Intel® SGX Operations 2 of 2

Operation

EREMOVE

EREPORT

ETRACK

EWB

EAUG

EMODPE

EMODPR

EMODT

EACCEPT

EACCEPTCOPY

Param Targ SECS Param SECS SECS

SRC VA SECS Targ SECS Targ SECI

NFO

Targ SEC

S

Targ SEC

S

Targ SECI

NFO

SECS Targ SR

C

SECI

NFO

EMODT

Targ

C

Y

C

C

C

C

C

Y

C

C

Y

C

Y

C

Y

Y

SECS

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Name

Type

Size (bits)

Description

TMP_SECS

Effective Address

32/64

Physical address of SECS to which EPC operand belongs.

SCRATCH_SECINFO

SECINFO

512

Scratch storage for holding the contents of DS:RBX.