41-42 Vol. 3D

SGX INSTRUCTION REFERENCES

Operation

Temp Variables in ELDB/ELDU Operational Flow

(* Check PAGEINFO and EPCPAGE alignment *)

IF ( (DS:RBX is not 32Byte Aligned) or (DS:RCX is not 4KByte Aligned) )

THEN #GP(0); FI;

IF (DS:RCX does not resolve within an EPC)

THEN #PF(DS:RCX); FI;

(* Check VASLOT alignment *)

IF (DS:RDX is not 8Byte aligned)

THEN #GP(0); FI;

IF (DS:RDX does not resolve within an EPC)

THEN #PF(DS:RDX); FI;

TMP_SRCPGE DS:RBX.SRCPGE;

TMP_SECS DS:RBX.SECS;

TMP_PCMD DS:RBXPCMD;

(* Check alignment of PAGEINFO (RBX)linked parameters. Note: PCMD pointer is overlaid on top of PAGEINFO.SECINFO field *)

IF ( (DS:TMP_PCMD is not 128Byte aligned) or (DS:TMP_SRCPGE is not 4KByte aligned) )

THEN #GP(0); FI;

(* Check concurrency of EPC and VASLOT by other Intel SGX instructions *)

IF ( (other instructions accessing EPC) or (Other instructions modifying VA slot) )

THEN #GP(0); FI;

(* Verify EPCM attributes of EPC page, VA, and SECS *)

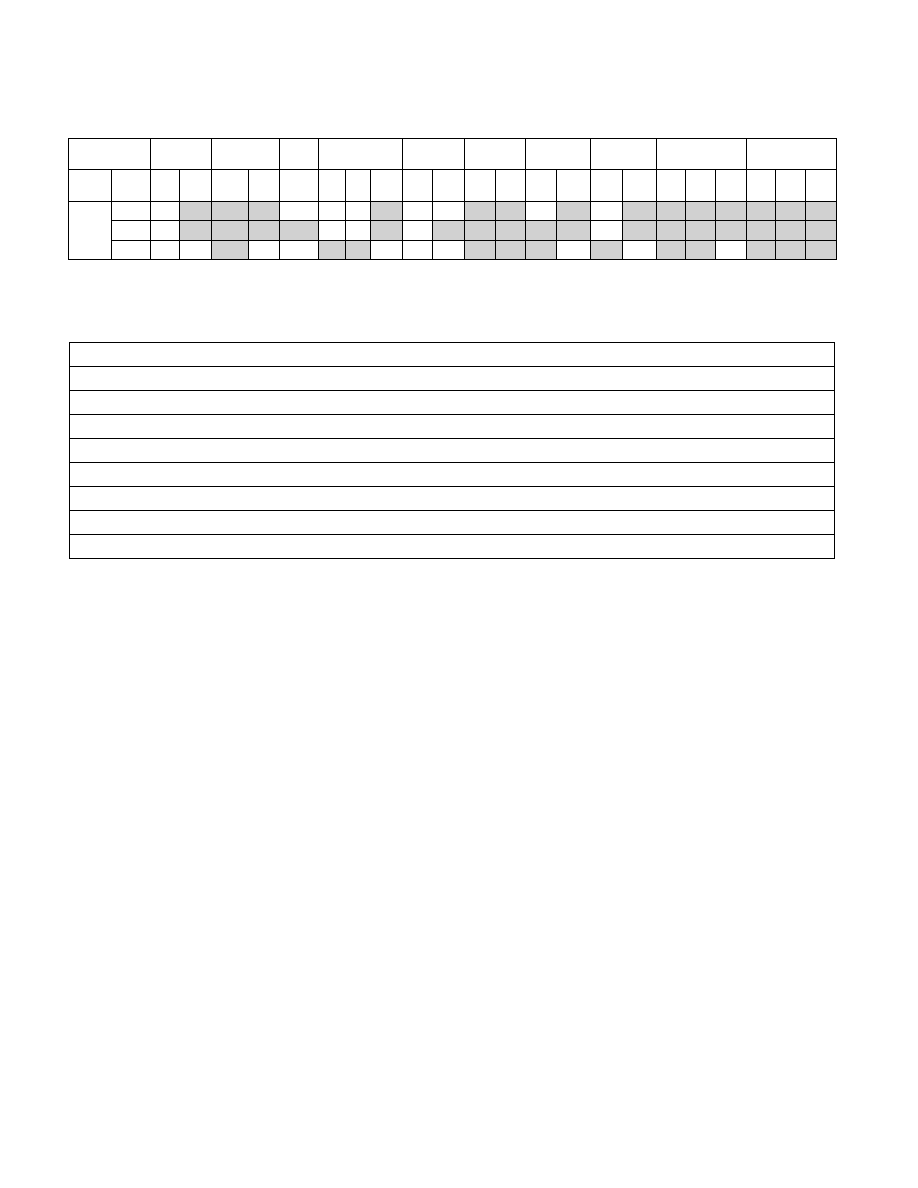

Table 41-27. Concurrency Restrictions of ELDB/ELDU with Intel® SGX Instructions - 2 of 2

Operation

EREMOVE

EREPORT

ETRA

CK

EWB

EAUG

EMODPE

EMODPR

EMODT

EACCEPT

EACCEPTCOPY

Param Targ SECS Param SECS SECS

SRC VA SECS Targ SECS Targ SECI

NFO

Targ SECS Targ SECS Targ SECI

NFO

SECS Targ SRC SECI

NFO

ELDB/E

LDU

Targ

N

N

N

N

N

N

N

N

VA

N

N

Y

N

N

SECS

N

Y

Y

Y

Y

N

Y

Y

Y

Y

Name

Type

Size (Bits)

Description

TMP_SRCPGE

Memory page

4KBytes

TMP_SECS

Memory page

4KBytes

TMP_PCMD

PCMD

128 Bytes

TMP_HEADER

MACHEADER

128 Bytes

TMP_VER

UINT64

64

TMP_MAC

UINT128

128

TMP_PK

UINT128

128

Page encryption/MAC key.

SCRATCH_PCMD

PCMD

128 Bytes