41-32 Vol. 3D

SGX INSTRUCTION REFERENCES

Operation

Temp Variables in EEXTEND Operational Flow

TMP_MODE64 ((IA32_EFER.LMA = 1) && (CS.L = 1));

IF (DS:RBX does resolve to an EPC page)

THEN #PF(DS:RBX); FI;

IF (DS:RCX is not 256Byte Aligned)

THEN #GP(0); FI;

IF (DS:RCX does not resolve within an EPC)

THEN #PF(DS:RCX); FI;

(* make sure no other Intel SGX instruction is accessing EPCM *)

IF (Other instructions accessing EPCM)

THEN #GP(0); FI;

IF (EPCM(DS:RCX). VALID = 0)

THEN #PF(DS:RCX); FI;

(* make sure that DS:RCX (DST) is pointing to a PT_REG or PT_TCS *)

IF ( (EPCM(DS:RCX).PT ≠ PT_REG) and (EPCM(DS:RCX).PT ≠ PT_TCS) )

THEN #PF(DS:RCX); FI;

TMP_SECS Get_SECS_ADDRESS();

IF (DS:RBX does not resolve to TMP_SECS)

THEN #GP(0); FI;

(* make sure no other instruction is accessing MRENCLAVE or ATTRIBUETS.INIT *)

IF ( (Other instruction accessing MRENCLAVE) or (Other instructions checking or updating the initialized state of the SECS))

THEN #GP(0); FI;

(* Calculate enclave offset *)

TMP_ENCLAVEOFFSET EPCM(DS:RCX).ENCLAVEADDRESS - TMP_SECS.BASEADDR;

TMP_ENCLAVEOFFSET TMP_ENCLAVEOFFSET + (DS:RCX & 0FFFH)

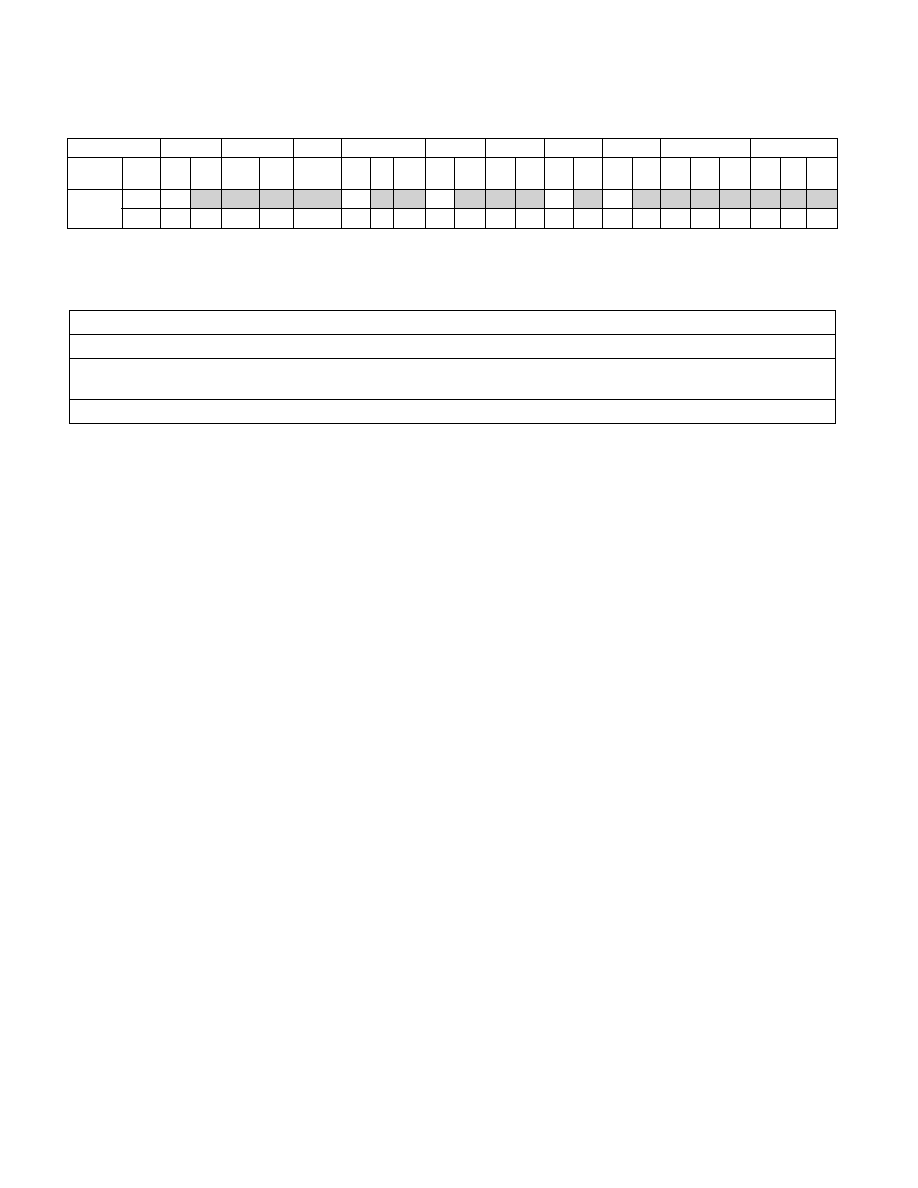

Table 41-21. Concurrency Restrictions of EEXTEND with Other Intel® SGX Operations 2 of 2

Operation

EREMOVE

EREPORT

ETRACK

EWB

EAUG

EMODPE

EMODPR

EMODT

EACCEPT

EACCEPTCOPY

Param Targ SECS Param SECS SECS

SRC VA SECS Targ SECS Targ SECI

NFO

Targ SEC

S

Targ SEC

S

Targ SECI

NFO

SECS Targ SR

C

SECI

NFO

EEXTEND Targ

N

N

N

N

N

SECS

Y

Y

Y

N

Y

Y

Y

Y

Y

N

Y

Y

Y

N

Y

N

Y

Y

N

Y

Y

Y

Name

Type

Size (Bits)

Description

TMP_SECS

64

Physical address of SECS of the enclave to which source operand belongs.

TMP_ENCLAVEOFFS

ET

Enclave Offset

64

The page displacement from the enclave base address.

TMPUPDATEFIELD

SHA256 Buffer 512

Buffer used to hold data being added to TMP_SECS.MRENCLAVE.