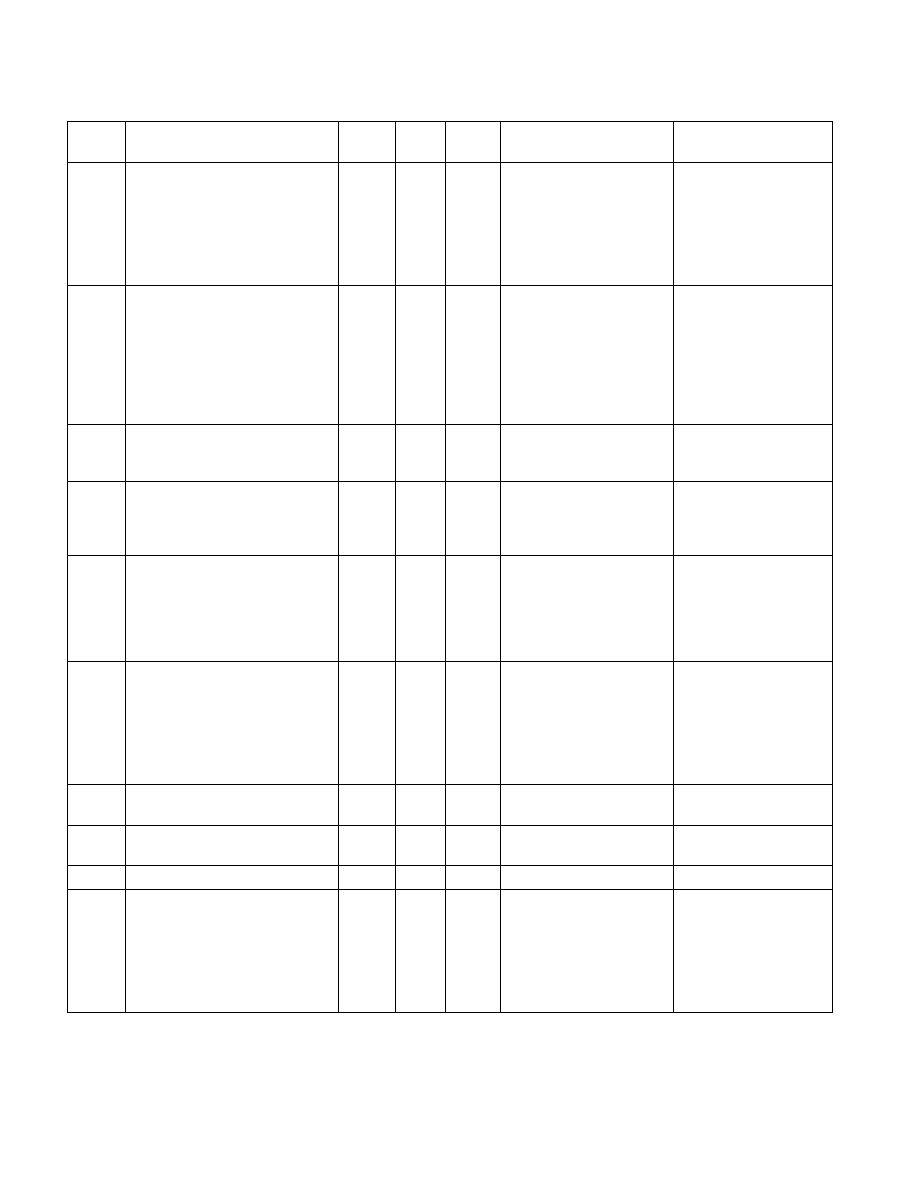

36-76 Vol. 3C

INTEL® PROCESSOR TRACE

16.13a

INIT (AP, goes to Wait-for-SIPI)

dc

0

0

See “INIT (AP, goes to

Wait-for-SIPI)” (cases

31[a-z] in Table 36-50)

for BranchEn packets that

precede

PWRE(C1), EXSTOP

16.13b

INIT (AP, goes to Wait-for-SIPI)

dc

dc

1

See “INIT (AP, goes to

Wait-for-SIPI)” (cases

31[a-z] in Table 36-50)

for BranchEn packets that

precede

PWRE(C1), EXSTOP(IP),

FUP(NLIP)

16.14a

Hardware Duty Cycling (HDC)

dc

0

0

* TSC if TSCEn=1

* TMA if TSCEn=MTCEn=1

PWRE(HW, C6), EXSTOP,

TSC?, TMA?, CBR,

PWRX(CC6, CC6, 0x8)

16.14b

Hardware Duty Cycling (HDC)

dc

dc

1

* TSC if TSCEn=1

* TMA if TSCEn=MTCEn=1

PWRE(HW, C6), EXS-

TOP(IP), FUP(NLIP), TSC?,

TMA?, CBR, PWRX(CC6,

CC6, 0x8)

16.15a

VM entry to HLT or Shutdown

dc

0

0

See “VM entry” (cases

17[a-z] in Table 36-50)

for BranchEn packets that

precede.

PWRE(C1), EXSTOP

16.15b

VM entry to HLT or Shutdown

dc

dc

1

See “VM entry” (cases

17[a-z] in Table 36-50)

for BranchEn packets that

precede.

PWRE(C1), EXSTOP(IP),

FUP(CLIP)

16.16a

EIST in C0, S1/TM1/TM2, or STP-

CLK#

dc

0

0

* TSC if TSCEn=1

* TMA if TSCEn=MTCEn=1

EXSTOP, TSC?, TMA?, CBR

16.16b

EIST in C0, S1/TM1/TM2, or STP-

CLK#

dc

dc

1

* TSC if TSCEn=1

* TMA if TSCEn=MTCEn=1

EXSTOP(IP), FUP(NLIP),

TSC?, TMA?, CBR

16.17

EIST in Cx (x>0)

dc

dc

dc

None

16.18

INTR during Cx (x>0)

dc

dc

dc

* TSC if TSCEn=1

* TMA if TSCEn=MTCEn=1

TSC?, TMA?, CBR,

PWRX(LCC, DCC, 0x1)

See “HW Interrupt” (cases

11[a-z] in Table 36-50)

for BranchEn packets that

follow.

Table 36-51. PwrEvtEn and PTWEn Packet Generation under Different Enable Conditions (Contd.)

Case

Operation

PktEn

Before

PktEn

After

CntxEn

After

Other Dependencies

Packets Output