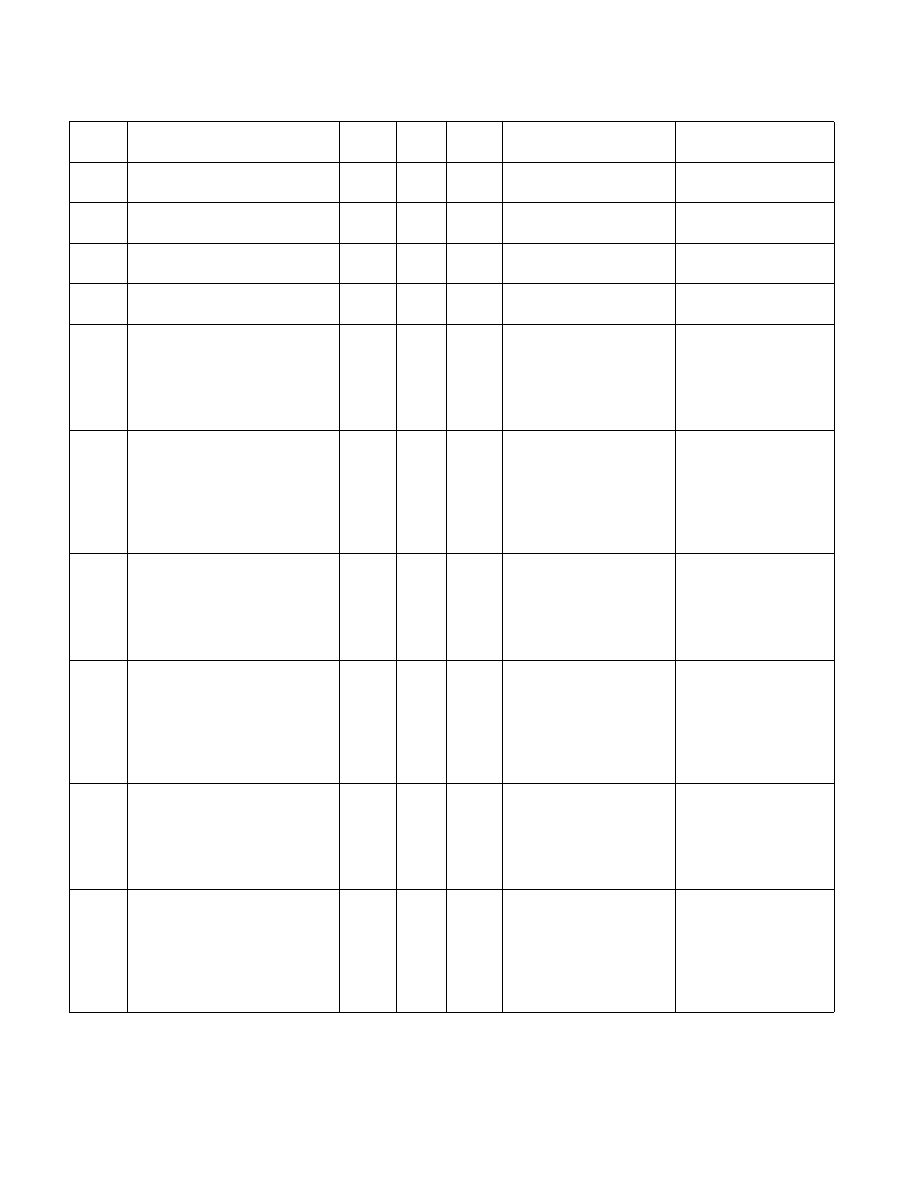

Vol. 3C 36-75

INTEL® PROCESSOR TRACE

16.6a

MWAIT(5) or I/O redir to MWAIT,

other thread(s) in core in C0/C1

dc

0

0

PWRE(C1), EXSTOP

16.6b

MWAIT(5) or I/O redir to MWAIT,

other thread(s) in core in C0/C1

dc

dc

1

MWAIT(5), PWRE(C1),

EXSTOP(IP), FUP(CLIP)

16.9a

HLT, Triple-fault shutdown, #MC

with CR4.MCE=0, RSM to Cx (x>0)

dc

0

0

PWRE(C1), EXSTOP

16.9b

HLT, Triple-fault shutdown, #MC

with CR4.MCE=1, RSM to Cx (x>0)

dc

dc

PWRE(C1), EXSTOP(IP),

FUP(CLIP)

16.10a

VMX abort

dc

0

0

See “VMX Abort” (cases

50) for BranchEn packets

that precede

PWRE(C1), EXSTOP

16.10b

VMX abort

dc

dc

1

See “VMX Abort” (cases

50) for BranchEn packets

that precede

PWRE(C1), EXSTOP(IP),

FUP(CLIP)

16.11a

RSM to Shutdown

dc

0

0

See “RSM to Shutdown”

(cases 15[def] in Table

36-50) for BranchEn

packets that precede

PWRE(C1), EXSTOP

16.11b

RSM to Shutdown

dc

dc

1

See “RSM to Shutdown”

(cases 15[def] in Table

36-50) for BranchEn

packets that precede

PWRE(C1), EXSTOP(IP),

FUP(CLIP)

16.12a

INIT (BSP)

dc

0

0

See “INIT (BSP)” (cases

30[a-z] in Table 36-50)

for packets that BranchEn

precede

PWRE(C1), EXSTOP

16.12b

INIT (BSP)

dc

dc

1

See “INIT (BSP)” (cases

30[a-z] in Table 36-50)

for packets that BranchEn

precede

PWRE(C1), EXSTOP(IP),

FUP(NLIP)

Table 36-51. PwrEvtEn and PTWEn Packet Generation under Different Enable Conditions (Contd.)

Case

Operation

PktEn

Before

PktEn

After

CntxEn

After

Other Dependencies

Packets Output