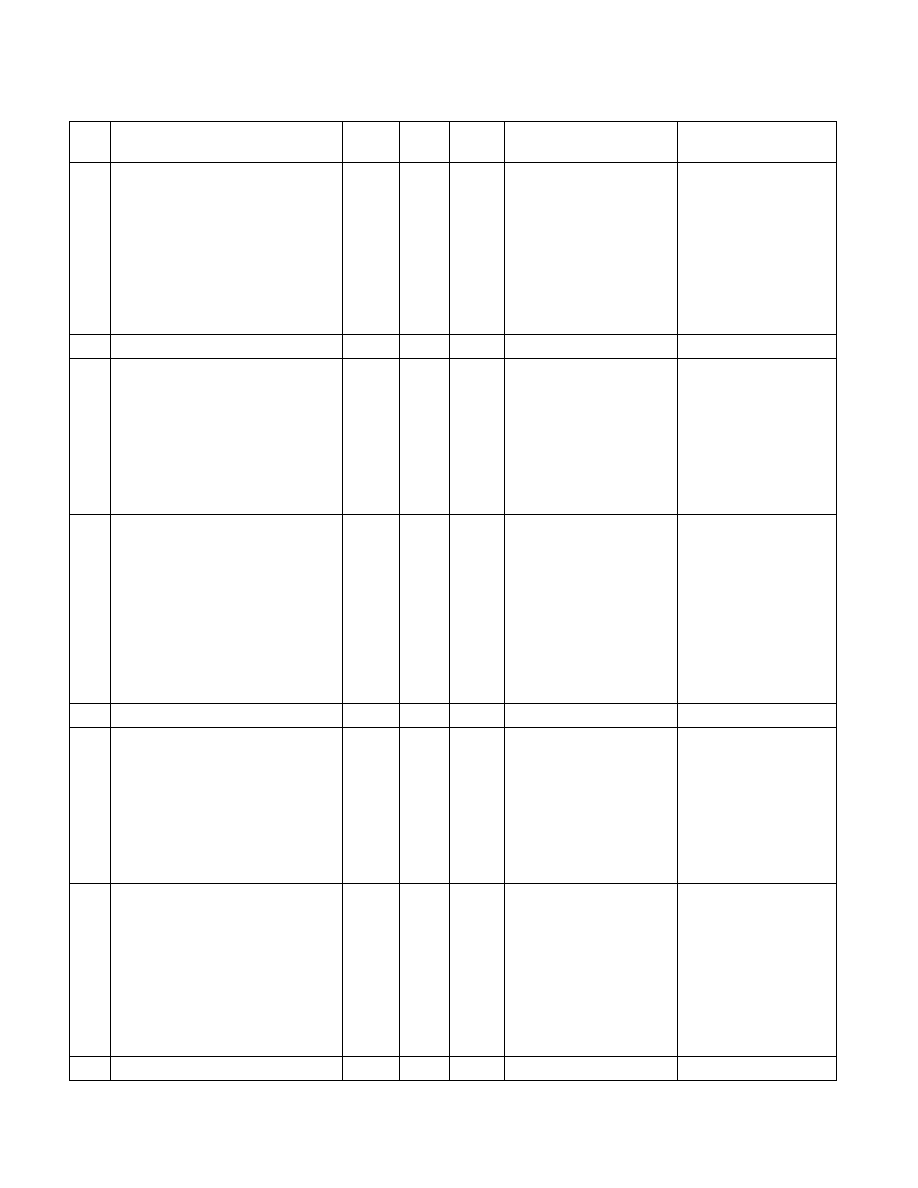

Vol. 3C 36-69

INTEL® PROCESSOR TRACE

11e

HW Interrupt

1

1

1

* PIP if CR3 is updated (i.e.,

task switch), and OS=1

*PIP.NR=1 if destination is

not root operation, and

“Conceal VMX non-root

operation from Intel PT”

execution control = 0;

* MODE.Exec if the opera-

tion changes CS.L/D or

IA32_EFER.LMA

FUP(NLIP), PIP(NewCR3,

NR?)?, MODE.Exec?,

TIP(BLIP)

12a

SW Interrupt

0

0

0

None

12f

SW Interrupt

0

0

1

* PIP if CR3 is updated (i.e.,

task switch), and OS=1

*PIP.NR=1 if destination is

not root operation, and

“Conceal VMX non-root

operation from Intel PT”

execution control = 0;

*TraceStop if BLIP is in a

TraceStop region

PIP(NewCR3, NR?)?,

TraceStop?

12b

SW Interrupt

0

1

1

* PIP if CR3 is updated (i.e.,

task switch), and OS=1

*PIP.NR=1 if destination is

not root operation, and

“Conceal VMX non-root

operation from Intel PT”

execution control = 0;

*MODE.Exec if the mode has

changed since the last

MODE.Exec, or if no

MODE.Exec since last PSB

PIP(NewCR3, NR?)?,

MODE.Exec?,

TIP.PGE(BLIP)

12c

SW Interrupt

1

0

0

FUP(CLIP), TIP.PGD()

12d

SW Interrupt

1

0

1

* PIP if CR3 is updated (i.e.,

task switch), and OS=1

*PIP.NR=1 if destination is

not root operation, and

“Conceal VMX non-root

operation from Intel PT”

execution control = 0;

*TraceStop if BLIP is in a

TraceStop region

FUP(CLIP), PIP(NewCR3,

NR?)?, TIP.PGD(BLIP),

TraceStop?

12e

SW Interrupt

1

1

1

* PIP if CR3 is updated (i.e.,

task switch), and OS=1

*PIP.NR=1 if destination is

not root operation, and

“Conceal VMX non-root

operation from Intel PT”

execution control = 0;

* MODE.Exec if the opera-

tion changes CS.L/D or

IA32_EFER.LMA

FUP(CLIP), PIP(NewCR3,

NR?)?, FUP(NLIP),

MODE.Exec?, TIP(BLIP)

13a

Exception/Fault

0

0

0

None

Table 36-50. Packet Generation under Different Enable Conditions (Contd.)

Case

Operation

PktEn

Before

PktEn

After

CntxEn

After

Other Dependencies

Packets Output