36-58 Vol. 3C

INTEL® PROCESSOR TRACE

36.4.2.22 Execution Stop (EXSTOP) Packet

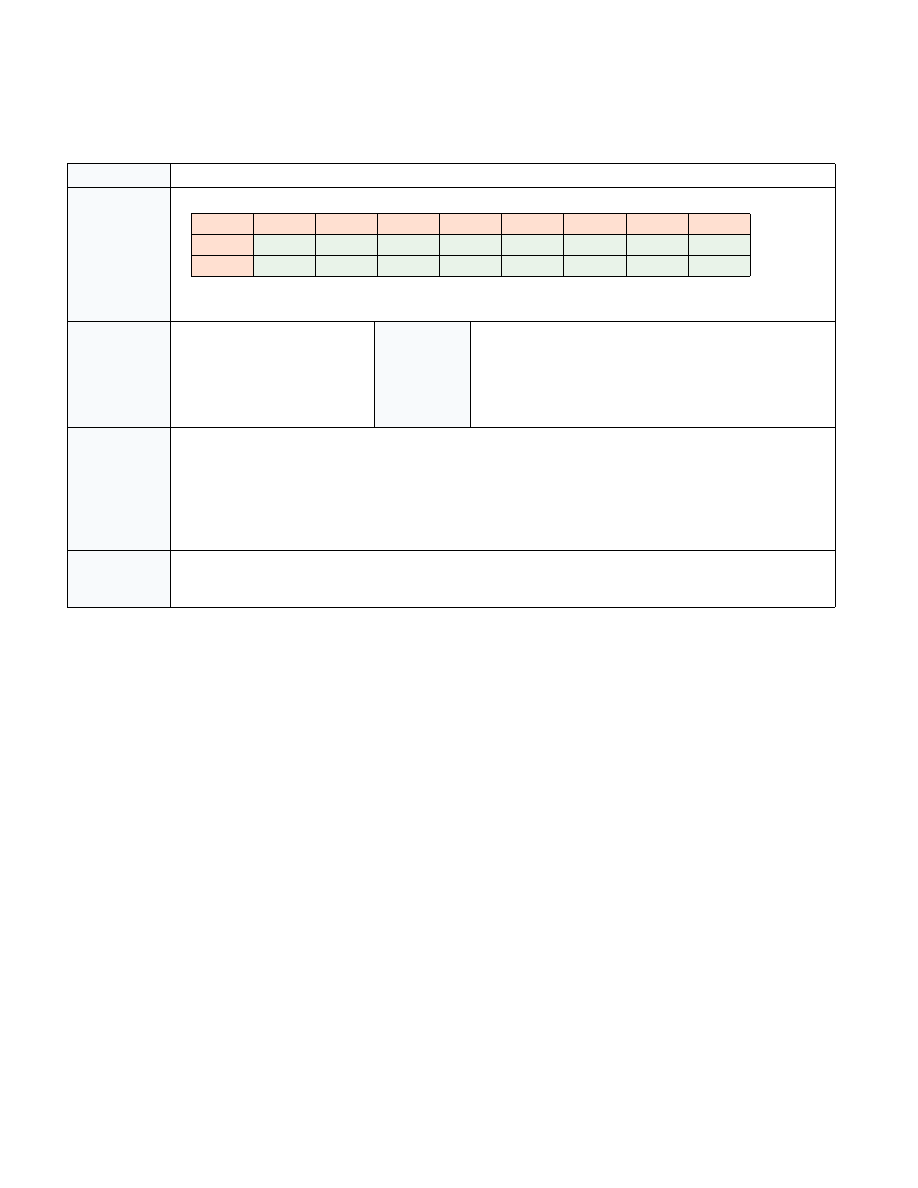

Table 36-41. EXSTOP Packet Definition

Name

EXSTOP Packet

Packet Format

Dependencies

TriggerEn & PwrEvtEn

Generation

Scenario

C-state entry, P-state change, or other processor clock power-

down. Includes :

• Entry to C-state deeper than C0.0

• TM1/2

• STPCLK#

• Frequency change due to IA32_CLOCK_MODULATION, Turbo

Description

This packet indicates that software execution has stopped due to processor clock powerdown. Later packets will

indicate when execution resumes.

If EXSTOP is generated while ContextEn is set, the IP bit will be set, and EXSTOP will be followed by a FUP packet

containing the IP at which execution stopped. More precisely, this will be the IP of the oldest instruction that has

not yet completed.

This packet is CYC-eligible, and hence will generate a CYC packet if IA32_RTIT_CTL.CYCEn=1 and any CYC Threshold

has been reached.

Application

If a FUP follows EXSTOP (hence IP bit set), the EXSTOP can be bound to the FUP IP. Otherwise the IP is not known.

Time of powerdown can be inferred from the preceding CYC, if CYCEn=1. Combined with the TSC at the time of

wake (if TSCEn=1), this can be used to determine the duration of the powerdown.

IP bit indicates if a FUP will follow.

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

1

0

1

IP

1

1

0

0

0

1

0