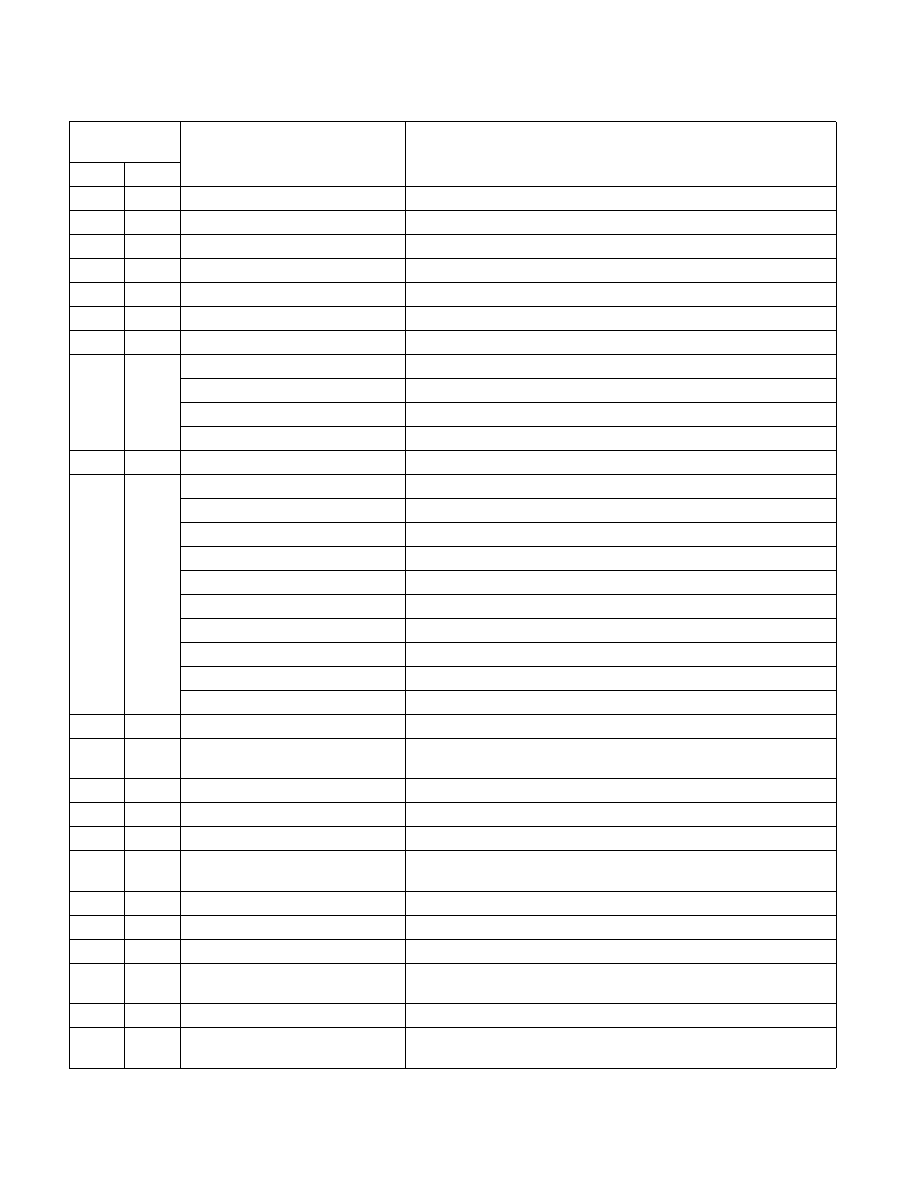

Vol. 3C 35-327

MODEL-SPECIFIC REGISTERS (MSRS)

269H

617

MTRRfix4K_C8000

26AH

618

MTRRfix4K_D0000

26BH

619

MTRRfix4K_D8000

26CH

620

MTRRfix4K_E0000

26DH

621

MTRRfix4K_E8000

26EH

622

MTRRfix4K_F0000

26FH

623

MTRRfix4K_F8000

2FFH

767

MTRRdefType

2:0

Default memory type

10

Fixed MTRR enable

11

MTRR Enable

400H

1024

MC0_CTL

401H

1025

MC0_STATUS

15:0

MC_STATUS_MCACOD

31:16

MC_STATUS_MSCOD

57

MC_STATUS_DAM

58

MC_STATUS_ADDRV

59

MC_STATUS_MISCV

60

MC_STATUS_EN. (Note: For MC0_STATUS only, this bit is hardcoded to 1.)

61

MC_STATUS_UC

62

MC_STATUS_O

63

MC_STATUS_V

402H

1026

MC0_ADDR

403H

1027

MC0_MISC

Defined in MCA architecture but not implemented in the P6 family

processors.

404H

1028

MC1_CTL

405H

1029

MC1_STATUS

Bit definitions same as MC0_STATUS.

406H

1030

MC1_ADDR

407H

1031

MC1_MISC

Defined in MCA architecture but not implemented in the P6 family

processors.

408H

1032

MC2_CTL

409H

1033

MC2_STATUS

Bit definitions same as MC0_STATUS.

40AH

1034

MC2_ADDR

40BH

1035

MC2_MISC

Defined in MCA architecture but not implemented in the P6 family

processors.

40CH

1036

MC4_CTL

40DH

1037

MC4_STATUS

Bit definitions same as MC0_STATUS, except bits 0, 4, 57, and 61 are

hardcoded to 1.

Table 35-46. MSRs in the P6 Family Processors (Contd.)

Register

Address

Register Name

Bit Description

Hex

Dec