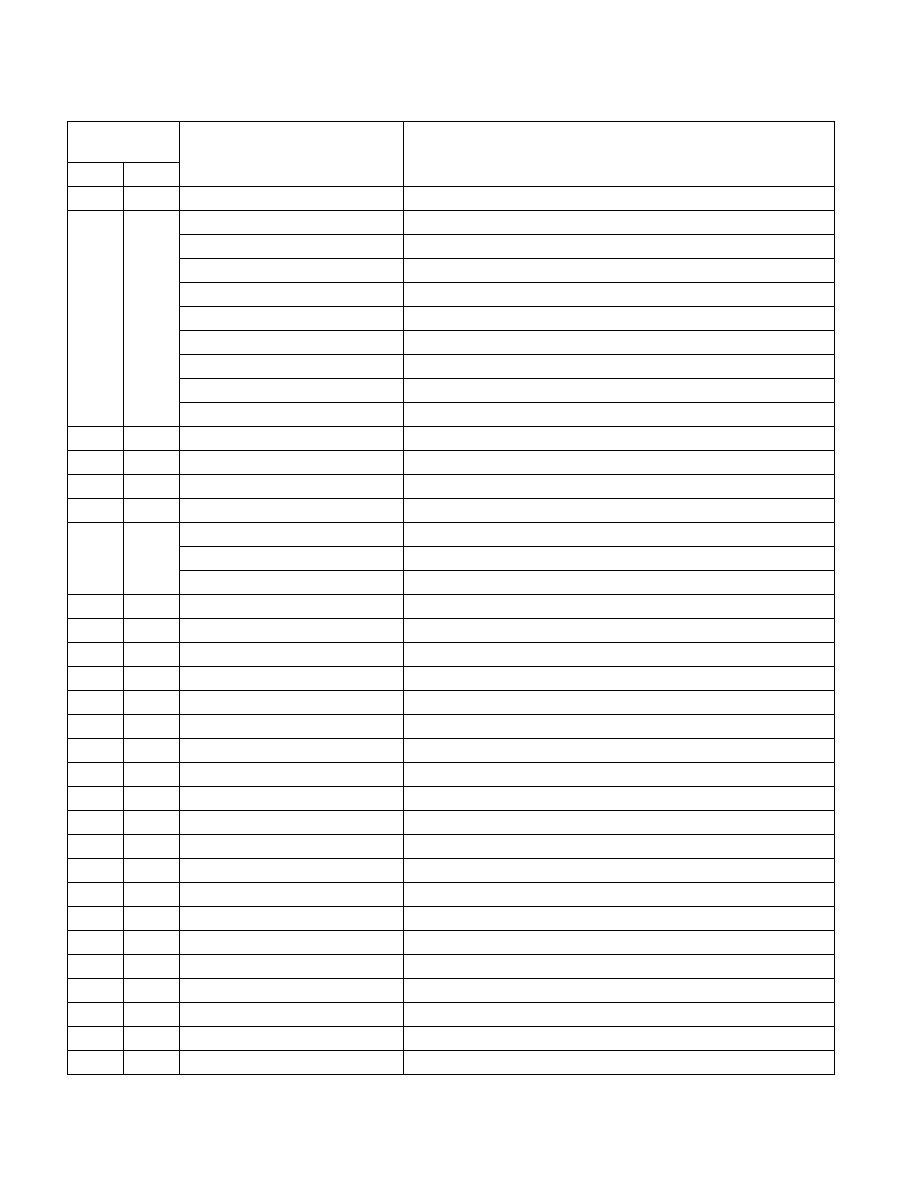

35-326 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

31:24

CMASK (Counter Mask)

1D9H

473

DEBUGCTLMSR

0

Enable/Disable Last Branch Records

1

Branch Trap Flag

2

Performance Monitoring/Break Point Pins

3

Performance Monitoring/Break Point Pins

4

Performance Monitoring/Break Point Pins

5

Performance Monitoring/Break Point Pins

6

Enable/Disable Execution Trace Messages

31:7

Reserved

1DBH

475

LASTBRANCHFROMIP

1DCH

476

LASTBRANCHTOIP

1DDH

477

LASTINTFROMIP

1DEH

478

LASTINTTOIP

1E0H

480

ROB_CR_BKUPTMPDR6

1:0

Reserved

2

Fast String Enable bit. Default is enabled

200H

512

MTRRphysBase0

201H

513

MTRRphysMask0

202H

514

MTRRphysBase1

203H

515

MTRRphysMask1

204H

516

MTRRphysBase2

205H

517

MTRRphysMask2

206H

518

MTRRphysBase3

207H

519

MTRRphysMask3

208H

520

MTRRphysBase4

209H

521

MTRRphysMask4

20AH

522

MTRRphysBase5

20BH

523

MTRRphysMask5

20CH

524

MTRRphysBase6

20DH

525

MTRRphysMask6

20EH

526

MTRRphysBase7

20FH

527

MTRRphysMask7

250H

592

MTRRfix64K_00000

258H

600

MTRRfix16K_80000

259H

601

MTRRfix16K_A0000

268H

616

MTRRfix4K_C0000

Table 35-46. MSRs in the P6 Family Processors (Contd.)

Register

Address

Register Name

Bit Description

Hex

Dec