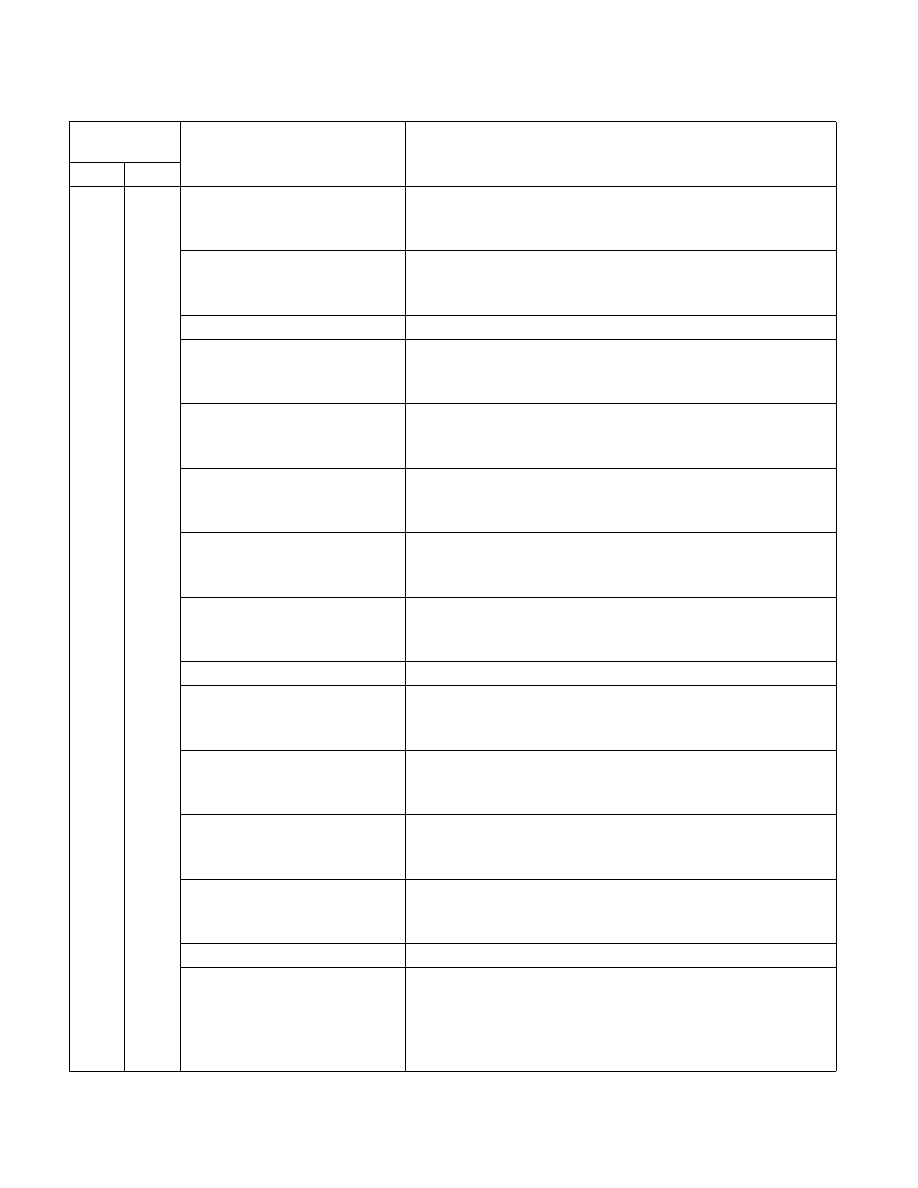

Vol. 3C 35-321

MODEL-SPECIFIC REGISTERS (MSRS)

3

AERR# Drive Enable (R/W)

1 = Enabled

0 = Disabled

4

BERR# Enable for Initiator Bus Requests (R/W)

1 = Enabled

0 = Disabled

5

Reserved.

6

BERR# Driver Enable for Initiator Internal Errors (R/W)

1 = Enabled

0 = Disabled

7

BINIT# Driver Enable (R/W)

1 = Enabled

0 = Disabled

8

Output Tri-state Enabled (R)

1 = Enabled

0 = Disabled

9

Execute BIST (R)

1 = Enabled

0 = Disabled

10

AERR# Observation Enabled (R)

1 = Enabled

0 = Disabled

11

Reserved.

12

BINIT# Observation Enabled (R)

1 = Enabled

0 = Disabled

13

In Order Queue Depth (R)

1 = 1

0 = 8

14

1-MByte Power on Reset Vector (R)

1 = 1MByte

0 = 4GBytes

15

FRC Mode Enable (R)

1 = Enabled

0 = Disabled

17:16

APIC Cluster ID (R)

19:18

System Bus Frequency (R)

00 = 66MHz

10 = 100Mhz

01 = 133MHz

11 = Reserved

Table 35-46. MSRs in the P6 Family Processors (Contd.)

Register

Address

Register Name

Bit Description

Hex

Dec