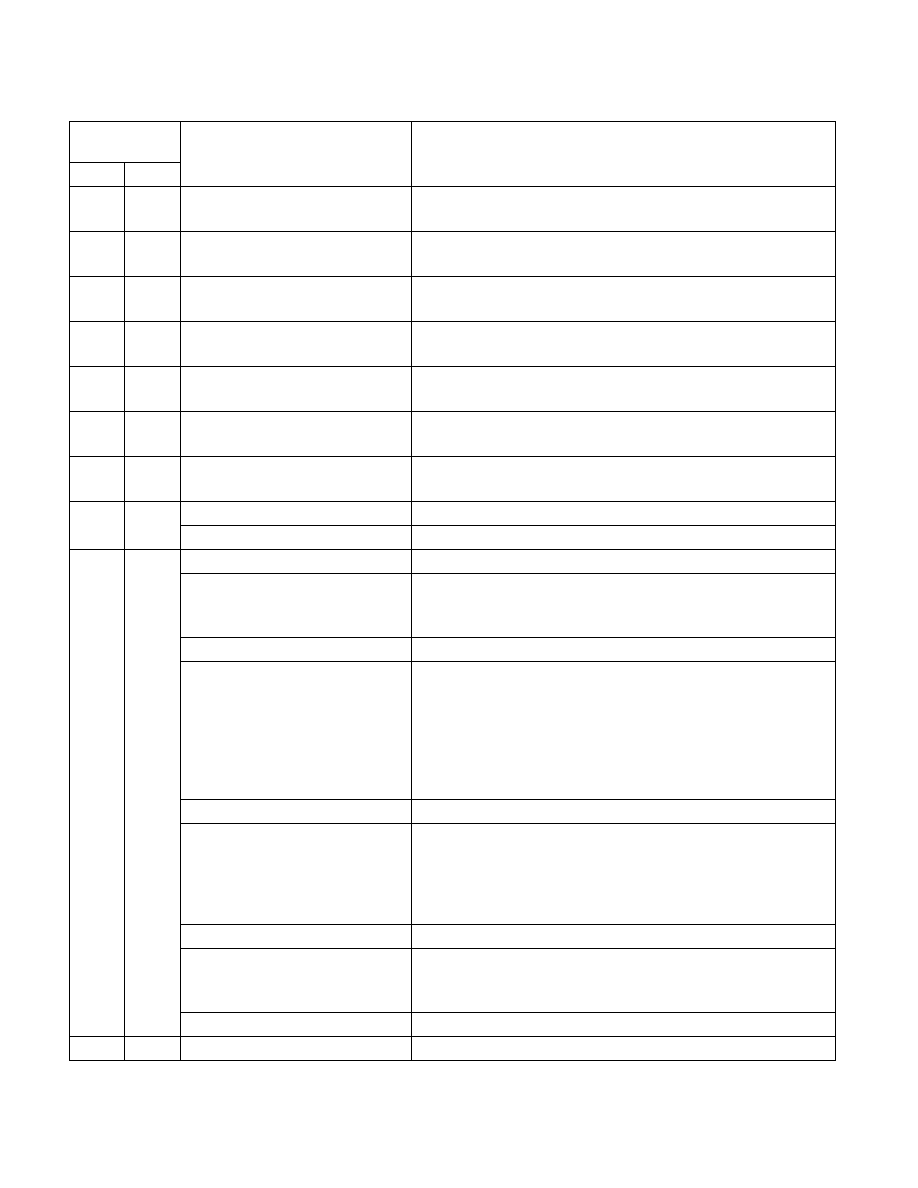

Vol. 3C 35-315

MODEL-SPECIFIC REGISTERS (MSRS)

41H

65

MSR_LASTBRANCH_1

Last Branch Record 1 (R/W)

See description of MSR_LASTBRANCH_0.

42H

66

MSR_LASTBRANCH_2

Last Branch Record 2 (R/W)

See description of MSR_LASTBRANCH_0.

43H

67

MSR_LASTBRANCH_3

Last Branch Record 3 (R/W)

See description of MSR_LASTBRANCH_0.

44H

68

MSR_LASTBRANCH_4

Last Branch Record 4 (R/W)

See description of MSR_LASTBRANCH_0.

45H

69

MSR_LASTBRANCH_5

Last Branch Record 5 (R/W)

See description of MSR_LASTBRANCH_0.

46H

70

MSR_LASTBRANCH_6

Last Branch Record 6 (R/W)

See description of MSR_LASTBRANCH_0.

47H

71

MSR_LASTBRANCH_7

Last Branch Record 7 (R/W)

See description of MSR_LASTBRANCH_0.

119H

281

MSR_BBL_CR_CTL

63:0

Reserved.

11EH

281

MSR_BBL_CR_CTL3

0

L2 Hardware Enabled (RO)

1 = If the L2 is hardware-enabled

0 = Indicates if the L2 is hardware-disabled

4:1

Reserved.

5

ECC Check Enable (RO)

This bit enables ECC checking on the cache data bus. ECC is always

generated on write cycles.

0 = Disabled (default)

1 = Enabled

For the Pentium M processor, ECC checking on the cache data bus is

always enabled.

7:6

Reserved.

8

L2 Enabled (R/W)

1 = L2 cache has been initialized

0 = Disabled (default)

Until this bit is set the processor will not respond to the WBINVD

instruction or the assertion of the FLUSH# input.

22:9

Reserved.

23

L2 Not Present (RO)

0 = L2 Present

1 = L2 Not Present

63:24

Reserved.

179H

377

IA32_MCG_CAP

Table 35-45. MSRs in Pentium M Processors (Contd.)

Register

Address

Register Name

Bit Description

Hex

Dec