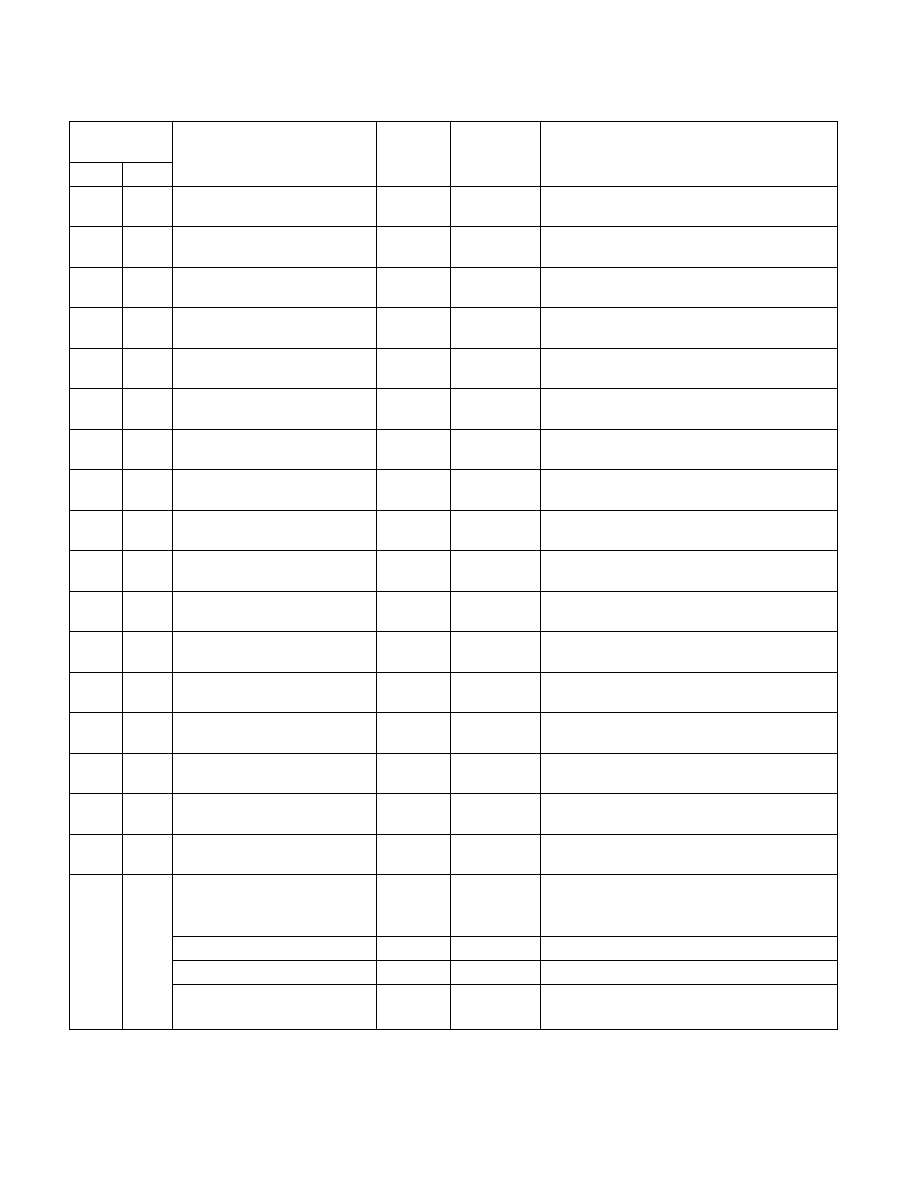

Vol. 3C 35-295

MODEL-SPECIFIC REGISTERS (MSRS)

3BDH

957

MSR_RAT_ESCR1

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3BEH

958

MSR_SSU_ESCR0

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3C0H

960

MSR_MS_ESCR0

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3C1H

961

MSR_MS_ESCR1

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3C2H

962

MSR_TBPU_ESCR0

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3C3H

963

MSR_TBPU_ESCR1

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3C4H

964

MSR_TC_ESCR0

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3C5H

965

MSR_TC_ESCR1

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3C8H

968

MSR_IX_ESCR0

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3C9H

969

MSR_IX_ESCR1

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3CAH

970

MSR_ALF_ESCR0

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3CBH

971

MSR_ALF_ESCR1

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3CCH

972

MSR_CRU_ESCR2

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3CDH

973

MSR_CRU_ESCR3

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3E0H

992

MSR_CRU_ESCR4

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3E1H

993

MSR_CRU_ESCR5

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3F0H

1008 MSR_TC_PRECISE_EVENT

0, 1, 2, 3,

4, 6

Shared

See Section 18.12.1, ‚ÄúESCR MSRs.‚ÄĚ

3F1H

1009 MSR_PEBS_ENABLE

0, 1, 2, 3,

4, 6

Shared

Processor Event Based Sampling (PEBS) (R/W)

Controls the enabling of processor event sampling

and replay tagging.

12:0

See Table 19-26.

23:13

Reserved.

24

UOP Tag

Enables replay tagging when set.

Table 35-41. MSRs in the Pentium¬ģ 4 and Intel¬ģ Xeon¬ģ Processors (Contd.)

Register

Address

Register Name

Fields and Flags

Model

Avail-

ability

Shared/

Unique

1

Bit Description

Hex

Dec