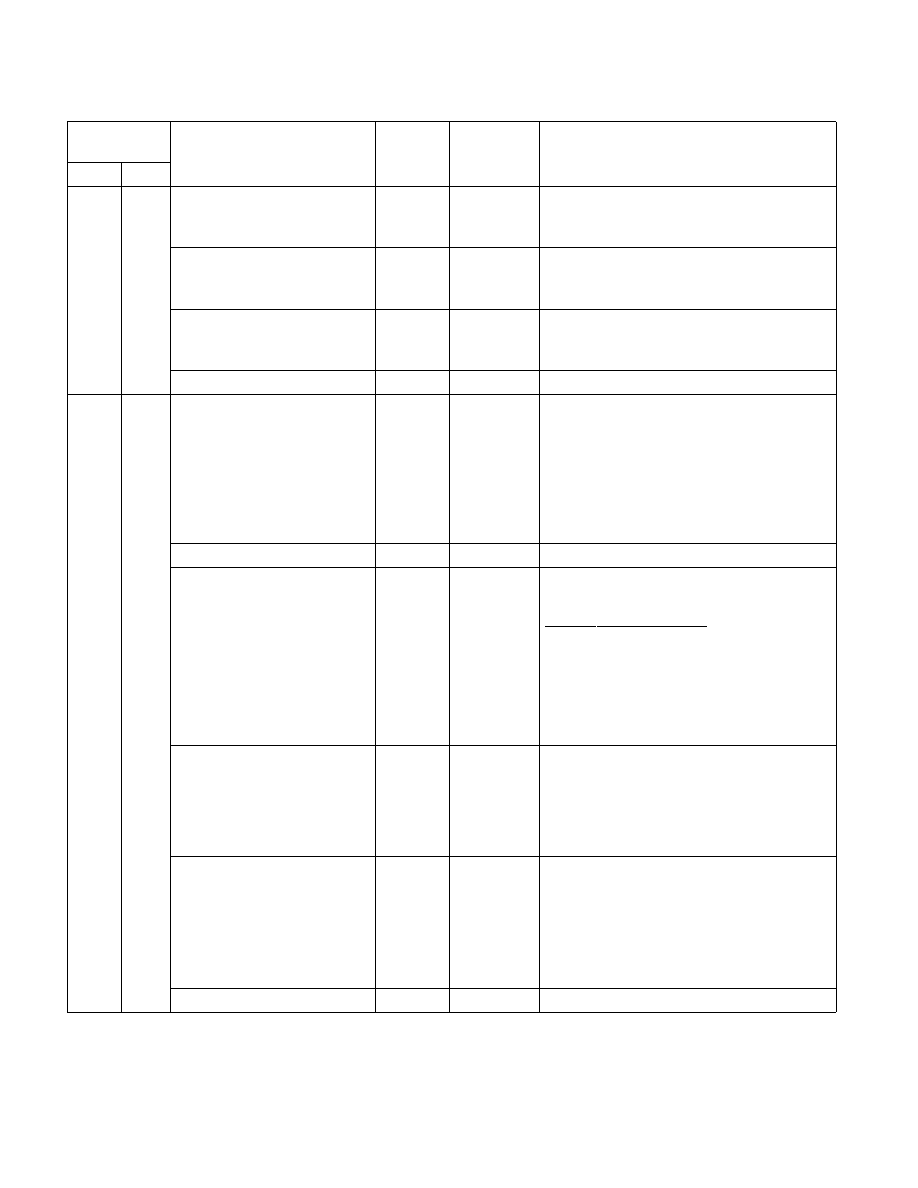

35-280 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

4

Initiator MCERR# Disable (R/W)

Set to disable MCERR# driving for initiator bus

requests (default); clear to enable.

5

Internal MCERR# Disable (R/W)

Set to disable MCERR# driving for initiator internal

errors (default); clear to enable.

6

BINIT# Driver Disable (R/W)

Set to disable BINIT# driver (default); clear to

enable driver.

63:7

Reserved.

2CH

44

MSR_EBC_FREQUENCY_ID

2,3, 4, 6

Shared

Processor Frequency Configuration

The bit field layout of this MSR varies according to

the MODEL value in the CPUID version

information. The following bit field layout applies

to Pentium 4 and Xeon Processors with MODEL

encoding equal or greater than 2.

(R) The field Indicates the current processor

frequency configuration.

15:0

Reserved.

18:16

Scalable Bus Speed (R/W)

Indicates the intended scalable bus speed:

EncodingScalable Bus Speed

000B

100 MHz (Model 2)

000B

266 MHz (Model 3 or 4)

001B

133 MHz

010B 200

MHz

011B 166

MHz

100B

333 MHz (Model 6)

133.33 MHz should be utilized if performing

calculation with System Bus Speed when encoding

is 001B.

166.67 MHz should be utilized if performing

calculation with System Bus Speed when encoding

is 011B.

266.67 MHz should be utilized if performing

calculation with System Bus Speed when encoding

is 000B and model encoding = 3 or 4.

333.33 MHz should be utilized if performing

calculation with System Bus Speed when encoding

is 100B and model encoding = 6.

All other values are reserved.

23:19

Reserved.

Table 35-41. MSRs in the Pentium® 4 and Intel® Xeon® Processors (Contd.)

Register

Address

Register Name

Fields and Flags

Model

Avail-

ability

Shared/

Unique

1

Bit Description

Hex

Dec