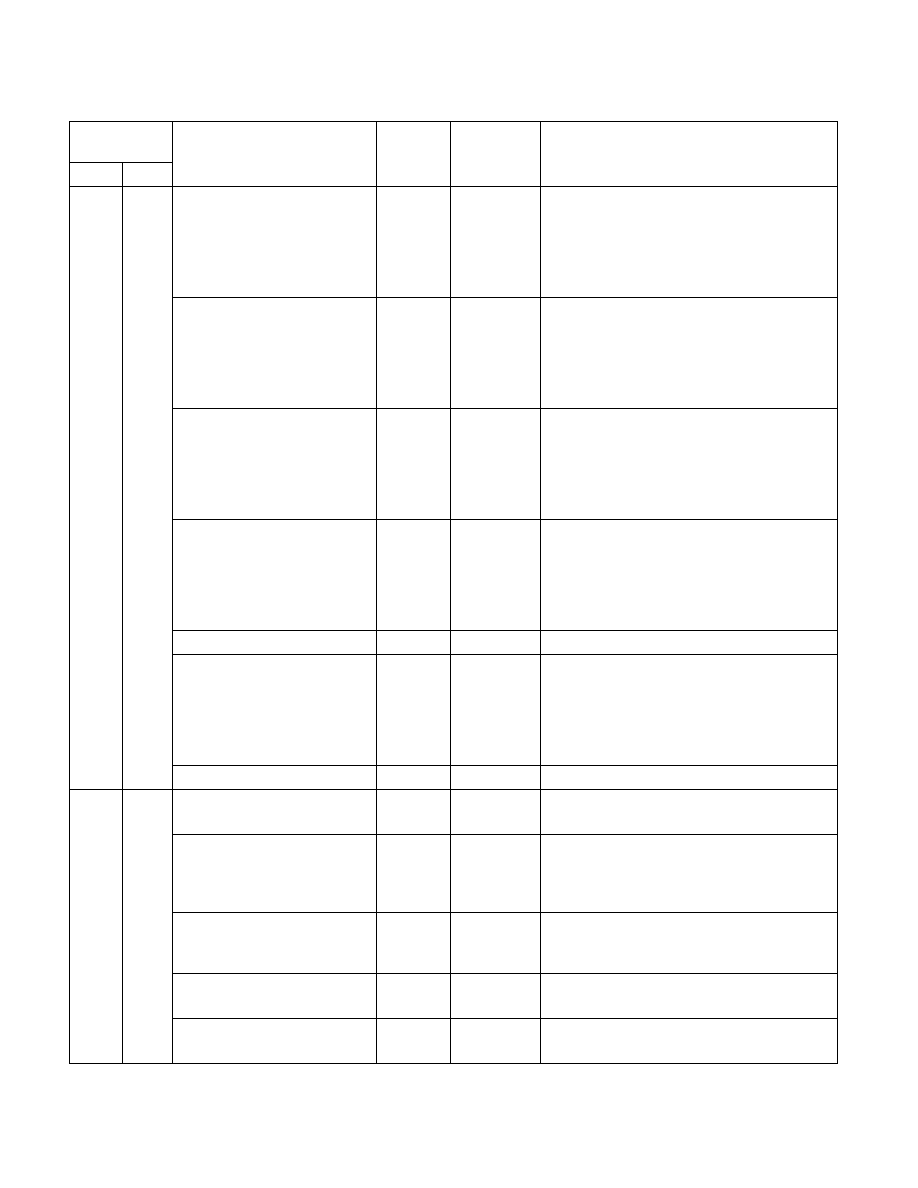

Vol. 3C 35-279

MODEL-SPECIFIC REGISTERS (MSRS)

3

MCERR# Observation Disabled (R)

Indicates whether MCERR# observation is enabled

(0) or disabled (1) as determined by the strapping

of A9#. The value in this bit is written on the

deassertion of RESET#; the bit is set to 1 when

the address bus signal is asserted.

4

BINIT# Observation Enabled (R)

Indicates whether BINIT# observation is enabled

(0) or disabled (1) as determined by the strapping

of A10#. The value in this bit is written on the

deassertion of RESET#; the bit is set to 1 when

the address bus signal is asserted.

6:5

APIC Cluster ID (R)

Contains the logical APIC cluster ID value as set by

the strapping of A12# and A11#. The logical

cluster ID value is written into the field on the

deassertion of RESET#; the field is set to 1 when

the address bus signal is asserted.

7

Bus Park Disable (R)

Indicates whether bus park is enabled (0) or

disabled (1) as set by the strapping of A15#. The

value in this bit is written on the deassertion of

RESET#; the bit is set to 1 when the address bus

signal is asserted.

11:8

Reserved.

13:12

Agent ID (R)

Contains the logical agent ID value as set by the

strapping of BR[3:0]. The logical ID value is

written into the field on the deassertion of

RESET#; the field is set to 1 when the address bus

signal is asserted.

63:14

Reserved.

2BH

43

MSR_EBC_SOFT_POWERON

0, 1, 2, 3,

4, 6

Shared

Processor Soft Power-On Configuration (R/W)

Enables and disables processor features.

0

RCNT/SCNT On Request Encoding Enable (R/W)

Controls the driving of RCNT/SCNT on the request

encoding. Set to enable (1); clear to disabled (0,

default).

1

Data Error Checking Disable (R/W)

Set to disable system data bus parity checking;

clear to enable parity checking.

2

Response Error Checking Disable (R/W)

Set to disable (default); clear to enable.

3

Address/Request Error Checking Disable (R/W)

Set to disable (default); clear to enable.

Table 35-41. MSRs in the Pentium® 4 and Intel® Xeon® Processors (Contd.)

Register

Address

Register Name

Fields and Flags

Model

Avail-

ability

Shared/

Unique

1

Bit Description

Hex

Dec