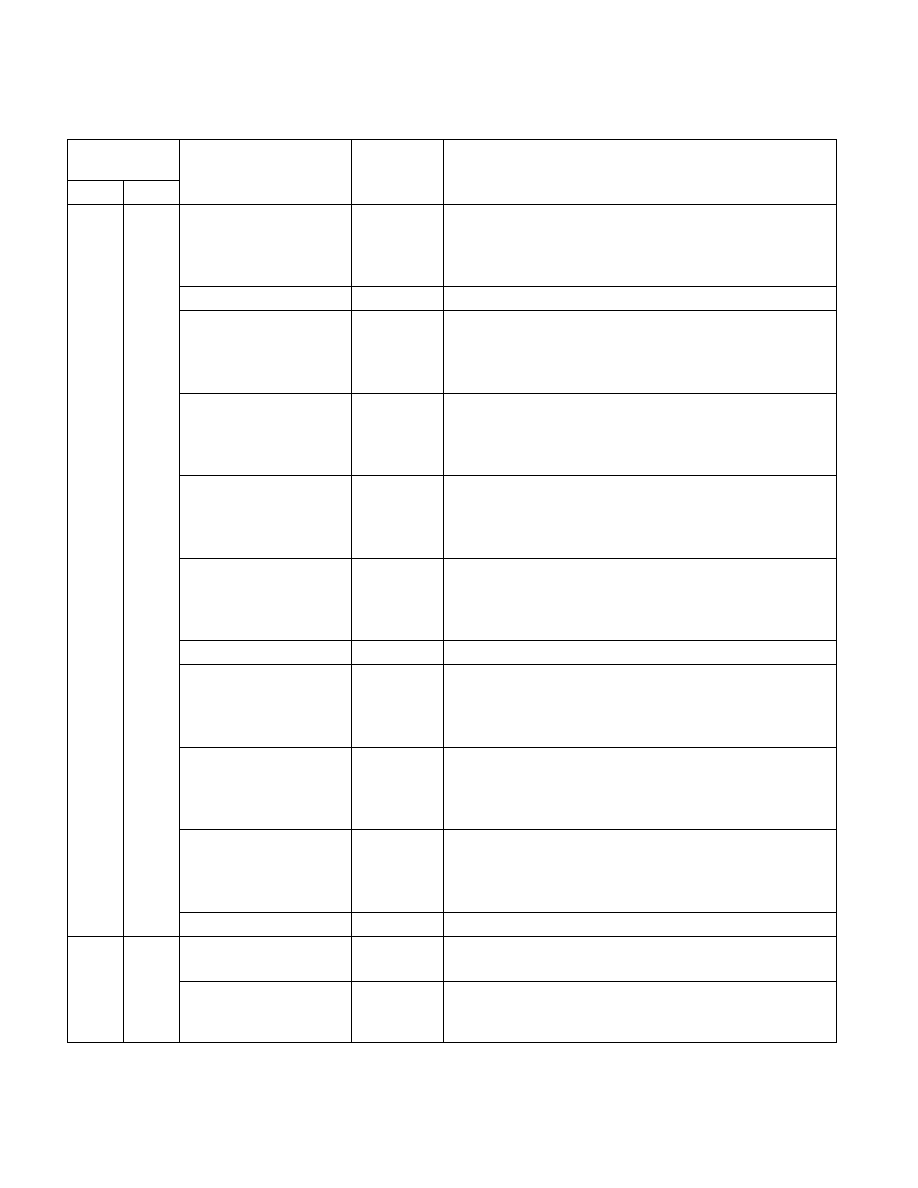

35-254 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

17

Thermal Log

When set, indicates that the Thermal Status bit has asserted since

the log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

20:18

Reserved.

21

Running Average Thermal Limit Log

When set, indicates that the RATL Status bit has asserted since the

log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

22

VR Therm Alert Log

When set, indicates that the VR Therm Alert Status bit has

asserted since the log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

23

VR Thermal Design Current Log

When set, indicates that the VR Therm Alert Status bit has

asserted since the log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

24

Other Log

When set, indicates that the OTHER Status bit has asserted since

the log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

25

Reserved

26

Package/Platform-Level PL1 Power Limiting Log

When set, indicates that the Package/Platform Level PL1 Power

Limiting Status bit has asserted since the log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

27

Package/Platform-Level PL2 Power Limiting Log

When set, indicates that the Package/Platform Level PL2 Power

Limiting Status bit has asserted since the log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

28

Inefficient Operation Log

When set, indicates that the Inefficient Operation Status bit has

asserted since the log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

63:29

Reserved.

6B1H

1713

MSR_RING_PERF_LIMIT_RE

ASONS

Package

Indicator of Frequency Clipping in the Ring Interconnect (R/W)

(frequency refers to ring interconnect in the uncore)

0

PROCHOT Status (R0)

When set, frequency is reduced due to assertion of external

PROCHOT.

Table 35-37. Additional MSRs Supported by 6th Generation Intel® Core™ Processors Based on Skylake

Microarchitecture

Register

Address

Register Name

Scope

Bit Description

Hex

Dec