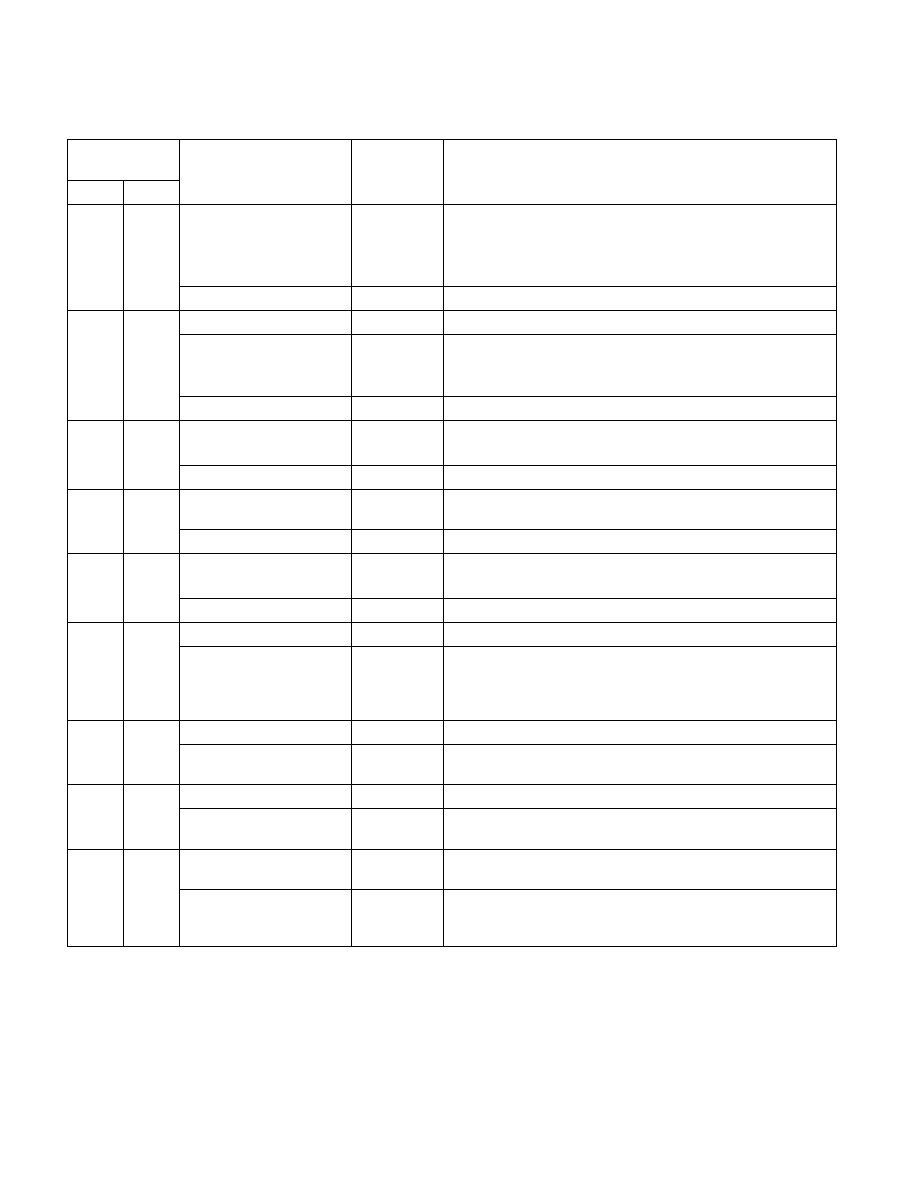

35-250 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

29

Turbo Transition Attenuation Log

When set, indicates that the Turbo Transition Attenuation Status

bit has asserted since the log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

63:30

Reserved.

652H

1618

MSR_PKG_HDC_CONFIG

Package

HDC Configuration (R/W).

2:0

PKG_Cx_Monitor.

Configures Package Cx state threshold for

MSR_PKG_HDC_DEEP_RESIDENCY

63: 3

Reserved

653H

1619

MSR_CORE_HDC_

RESIDENCY

Core

Core HDC Idle Residency. (R/O).

63:0

Core_Cx_Duty_Cycle_Cnt.

655H

1621

MSR_PKG_HDC_SHALLOW_

RESIDENCY

Package

Accumulate the cycles the package was in C2 state and at least one

logical processor was in forced idle. (R/O).

63:0

Pkg_C2_Duty_Cycle_Cnt.

656H

1622

MSR_PKG_HDC_DEEP_

RESIDENCY

Package

Package Cx HDC Idle Residency. (R/O).

63:0

Pkg_Cx_Duty_Cycle_Cnt.

658H

1624

MSR_WEIGHTED_CORE_C0

Package

Core-count Weighted C0 Residency. (R/O).

63:0

Increment at the same rate as the TSC. The increment each cycle is

weighted by the number of processor cores in the package that

reside in C0. If N cores are simultaneously in C0, then each cycle the

counter increments by N.

659H

1625

MSR_ANY_CORE_C0

Package

Any Core C0 Residency. (R/O)

63:0

Increment at the same rate as the TSC. The increment each cycle is

one if any processor core in the package is in C0.

65AH

1626

MSR_ANY_GFXE_C0

Package

Any Graphics Engine C0 Residency. (R/O)

63:0

Increment at the same rate as the TSC. The increment each cycle is

one if any processor graphic device’s compute engines are in C0.

65BH

1627

MSR_CORE_GFXE_OVERLA

P_C0

Package

Core and Graphics Engine Overlapped C0 Residency. (R/O)

63:0

Increment at the same rate as the TSC. The increment each cycle is

one if at least one compute engine of the processor graphics is in

C0 and at least one processor core in the package is also in C0.

Table 35-37. Additional MSRs Supported by 6th Generation Intel® Core™ Processors Based on Skylake

Microarchitecture

Register

Address

Register Name

Scope

Bit Description

Hex

Dec