35-208 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

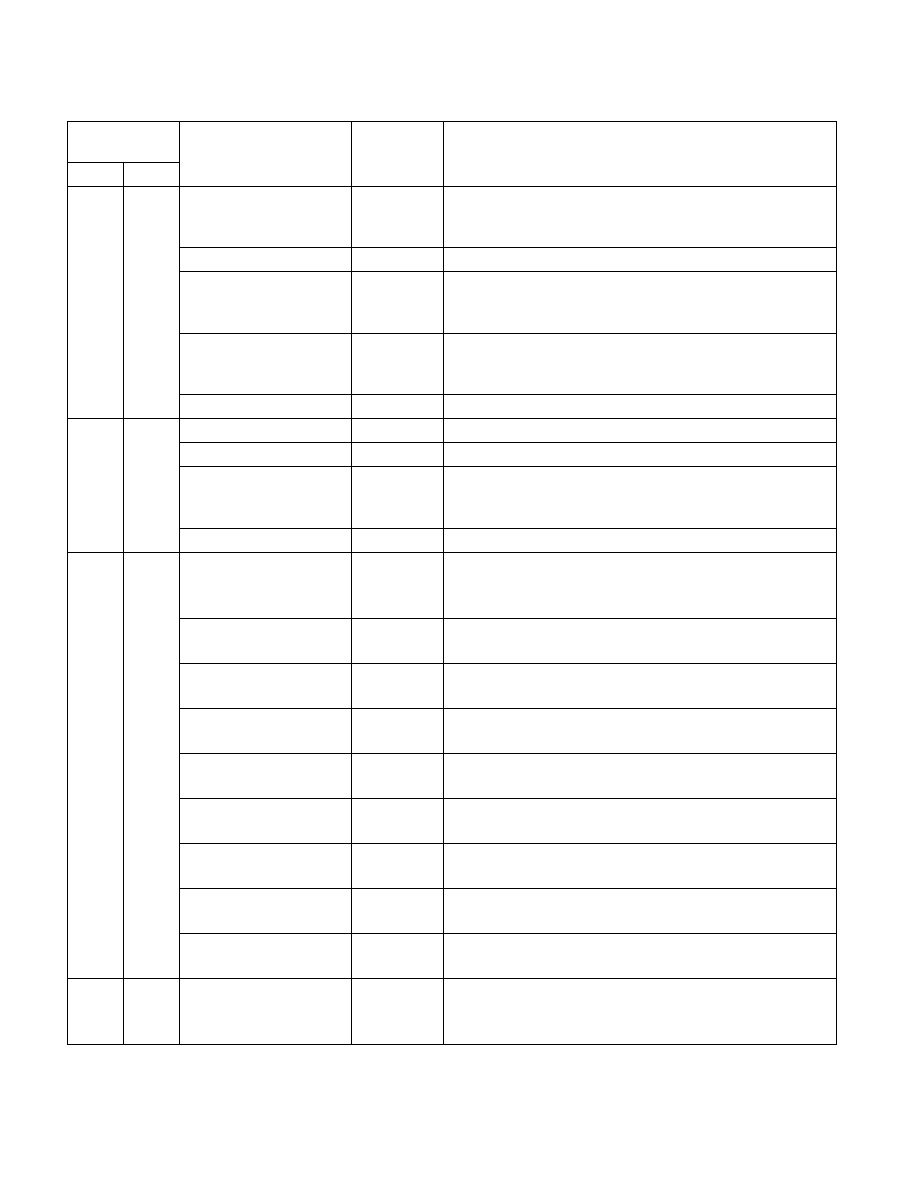

17DH

390

MSR_SMM_MCA_CAP

THREAD

Enhanced SMM Capabilities (SMM-RO)

Reports SMM capability Enhancement. Accessible only while in

SMM.

57:0

Reserved

58

SMM_Code_Access_Chk (SMM-RO)

If set to 1 indicates that the SMM code access restriction is

supported and a host-space interface available to SMM handler.

59

Long_Flow_Indication (SMM-RO)

If set to 1 indicates that the SMM long flow indicator is supported

and a host-space interface available to SMM handler.

63:60

Reserved

17FH

383

MSR_ERROR_CONTROL

Package

MC Bank Error Configuration (R/W)

0

Reserved

1

MemError Log Enable (R/W)

When set, enables IMC status bank to log additional info in bits

36:32.

63:2

Reserved.

1ADH

429

MSR_TURBO_RATIO_LIMIT

Package

Maximum Ratio Limit of Turbo Mode

RO if MSR_PLATFORM_INFO.[28] = 0,

RW if MSR_PLATFORM_INFO.[28] = 1

7:0

Package

Maximum Ratio Limit for 1C

Maximum turbo ratio limit of 1 core active.

15:8

Package

Maximum Ratio Limit for 2C

Maximum turbo ratio limit of 2 core active.

23:16

Package

Maximum Ratio Limit for 3C

Maximum turbo ratio limit of 3 core active.

31:24

Package

Maximum Ratio Limit for 4C

Maximum turbo ratio limit of 4 core active.

39:32

Package

Maximum Ratio Limit for 5C

Maximum turbo ratio limit of 5 core active.

47:40

Package

Maximum Ratio Limit for 6C

Maximum turbo ratio limit of 6 core active.

55:48

Package

Maximum Ratio Limit for 7C

Maximum turbo ratio limit of 7 core active.

63:56

Package

Maximum Ratio Limit for 8C

Maximum turbo ratio limit of 8 core active.

1AEH

430

MSR_TURBO_RATIO_LIMIT1 Package

Maximum Ratio Limit of Turbo Mode

RO if MSR_PLATFORM_INFO.[28] = 0,

RW if MSR_PLATFORM_INFO.[28] = 1

Table 35-30. Additional MSRs Supported by Intel® Xeon® Processor E5 v3 Family

Register

Address

Register Name

Scope

Bit Description

Hex

Dec