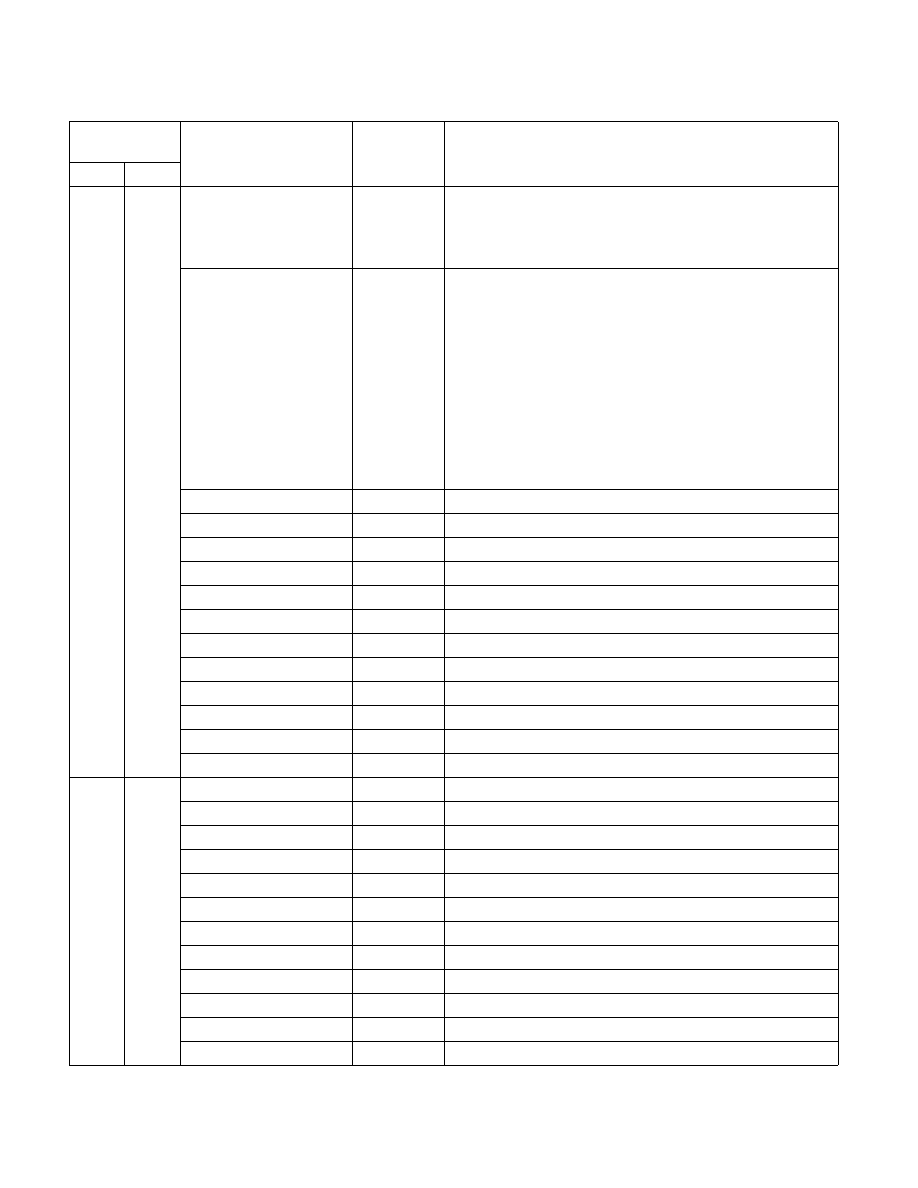

Vol. 3C 35-207

MODEL-SPECIFIC REGISTERS (MSRS)

E2H

226

MSR_PKG_CST_CONFIG_

CONTROL

Core

C-State Configuration Control (R/W)

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-states.

See http://biosbits.org.

2:0

Package C-State Limit (R/W)

Specifies the lowest processor-specific C-state code name

(consuming the least power) for the package. The default is set as

factory-configured package C-state limit.

The following C-state code name encodings are supported:

000b: C0/C1 (no package C-state support)

001b: C2

010b: C6 (non-retention)

011b: C6 (retention)

111b: No Package C state limits. All C states supported by the

processor are available.

9:3

Reserved

10

I/O MWAIT Redirection Enable (R/W)

14:11

Reserved

15

CFG Lock (R/WO)

24:16

Reserved

25

C3 State Auto Demotion Enable (R/W)

26

C1 State Auto Demotion Enable (R/W)

27

Enable C3 Undemotion (R/W)

28

Enable C1 Undemotion (R/W)

29

Package C State Demotion Enable (R/W)

30

Package C State UnDemotion Enable (R/W)

63:31

Reserved

179H

377

IA32_MCG_CAP

Thread

Global Machine Check Capability (R/O)

7:0

Count

8

MCG_CTL_P

9

MCG_EXT_P

10

MCP_CMCI_P

11

MCG_TES_P

15:12

Reserved.

23:16

MCG_EXT_CNT

24

MCG_SER_P

25

MCG_EM_P

26

MCG_ELOG_P

63:27

Reserved.

Table 35-30. Additional MSRs Supported by Intel® Xeon® Processor E5 v3 Family

Register

Address

Register Name

Scope

Bit Description

Hex

Dec