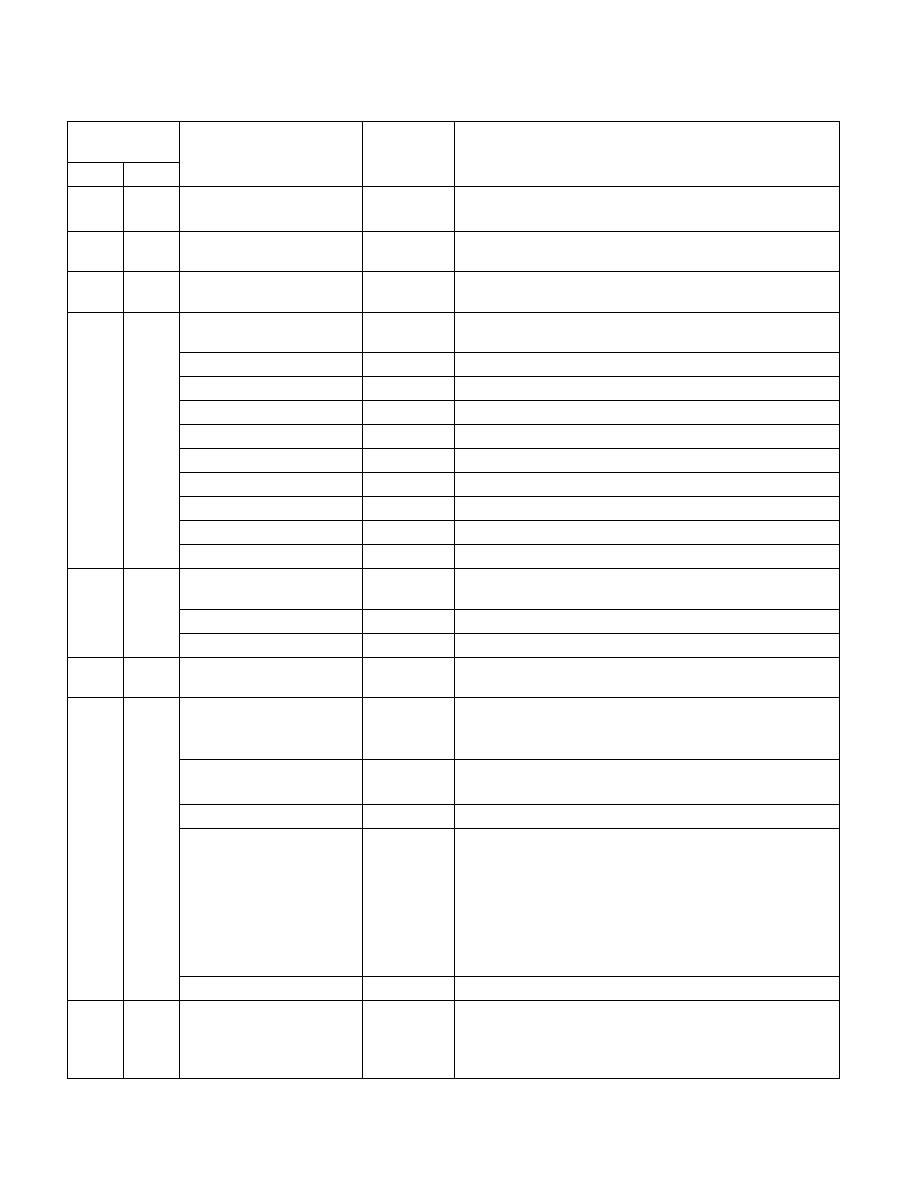

35-196 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

3B1H

947

MSR_UNC_ARB_PERFCTR1

Package

Uncore Arb unit, performance counter 1

3B2H

944

MSR_UNC_ARB_

PERFEVTSEL0

Package

Uncore Arb unit, counter 0 event select MSR

3B3H

945

MSR_UNC_ARB_

PERFEVTSEL1

Package

Uncore Arb unit, counter 1 event select MSR

391H

913

MSR_UNC_PERF_GLOBAL_

CTRL

Package

Uncore PMU global control

0

Core 0 select

1

Core 1 select

2

Core 2 select

3

Core 3 select

18:4

Reserved.

29

Enable all uncore counters

30

Enable wake on PMI

31

Enable Freezing counter when overflow

63:32

Reserved.

395H

917

MSR_UNC_PERF_FIXED_

CTR

Package

Uncore fixed counter

47:0

Current count

63:48

Reserved.

3B3H

945

MSR_UNC_ARB_

PERFEVTSEL1

Package

Uncore Arb unit, counter 1 event select MSR

4E0H

1248

MSR_SMM_FEATURE_CONTR

OL

Package

Enhanced SMM Feature Control (SMM-RW)

Reports SMM capability Enhancement. Accessible only while in

SMM.

0

Lock (SMM-RWO)

When set to ‘1’ locks this register from further changes

1

Reserved

2

SMM_Code_Chk_En (SMM-RW)

This control bit is available only if MSR_SMM_MCA_CAP[58] == 1.

When set to ‘0’ (default) none of the logical processors are

prevented from executing SMM code outside the ranges defined

by the SMRR.

When set to ‘1’ any logical processor in the package that attempts

to execute SMM code not within the ranges defined by the SMRR

will assert an unrecoverable MCE.

63:3

Reserved

4E2H

1250

MSR_SMM_DELAYED

Package

SMM Delayed (SMM-RO)

Reports the interruptible state of all logical processors in the

package. Available only while in SMM and

MSR_SMM_MCA_CAP[LONG_FLOW_INDICATION] == 1.

Table 35-28. MSRs Supported by 4th Generation Intel® Core™ Processors (Haswell microarchitecture) (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec