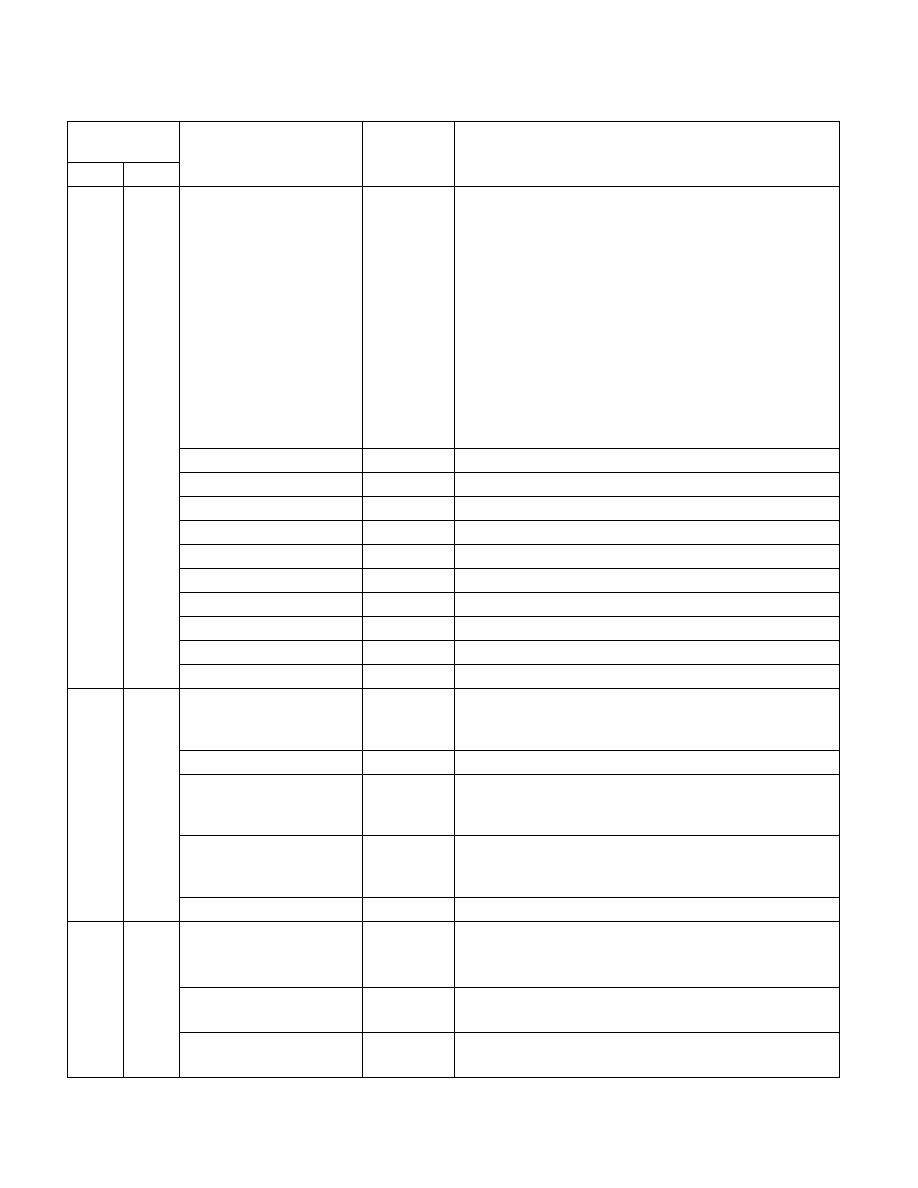

35-194 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

3:0

Package C-State Limit (R/W)

Specifies the lowest processor-specific C-state code name

(consuming the least power) for the package. The default is set as

factory-configured package C-state limit.

The following C-state code name encodings are supported:

0000b: C0/C1 (no package C-state support)

0001b: C2

0010b: C3

0011b: C6

0100b: C7

0101b: C7s

Package C states C7 are not available to processor with signature

06_3CH

9:4

Reserved

10

I/O MWAIT Redirection Enable (R/W)

14:11

Reserved

15

CFG Lock (R/WO)

24:16

Reserved

25

C3 State Auto Demotion Enable (R/W)

26

C1 State Auto Demotion Enable (R/W)

27

Enable C3 Undemotion (R/W)

28

Enable C1 Undemotion (R/W)

63:29

Reserved

17DH

390

MSR_SMM_MCA_CAP

THREAD

Enhanced SMM Capabilities (SMM-RO)

Reports SMM capability Enhancement. Accessible only while in

SMM.

57:0

Reserved

58

SMM_Code_Access_Chk (SMM-RO)

If set to 1 indicates that the SMM code access restriction is

supported and the MSR_SMM_FEATURE_CONTROL is supported.

59

Long_Flow_Indication (SMM-RO)

If set to 1 indicates that the SMM long flow indicator is supported

and the MSR_SMM_DELAYED is supported.

63:60

Reserved

1ADH

429

MSR_TURBO_RATIO_LIMIT

Package

Maximum Ratio Limit of Turbo Mode

RO if MSR_PLATFORM_INFO.[28] = 0,

RW if MSR_PLATFORM_INFO.[28] = 1

7:0

Package

Maximum Ratio Limit for 1C

Maximum turbo ratio limit of 1 core active.

15:8

Package

Maximum Ratio Limit for 2C

Maximum turbo ratio limit of 2 core active.

Table 35-28. MSRs Supported by 4th Generation Intel® Core™ Processors (Haswell microarchitecture) (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec