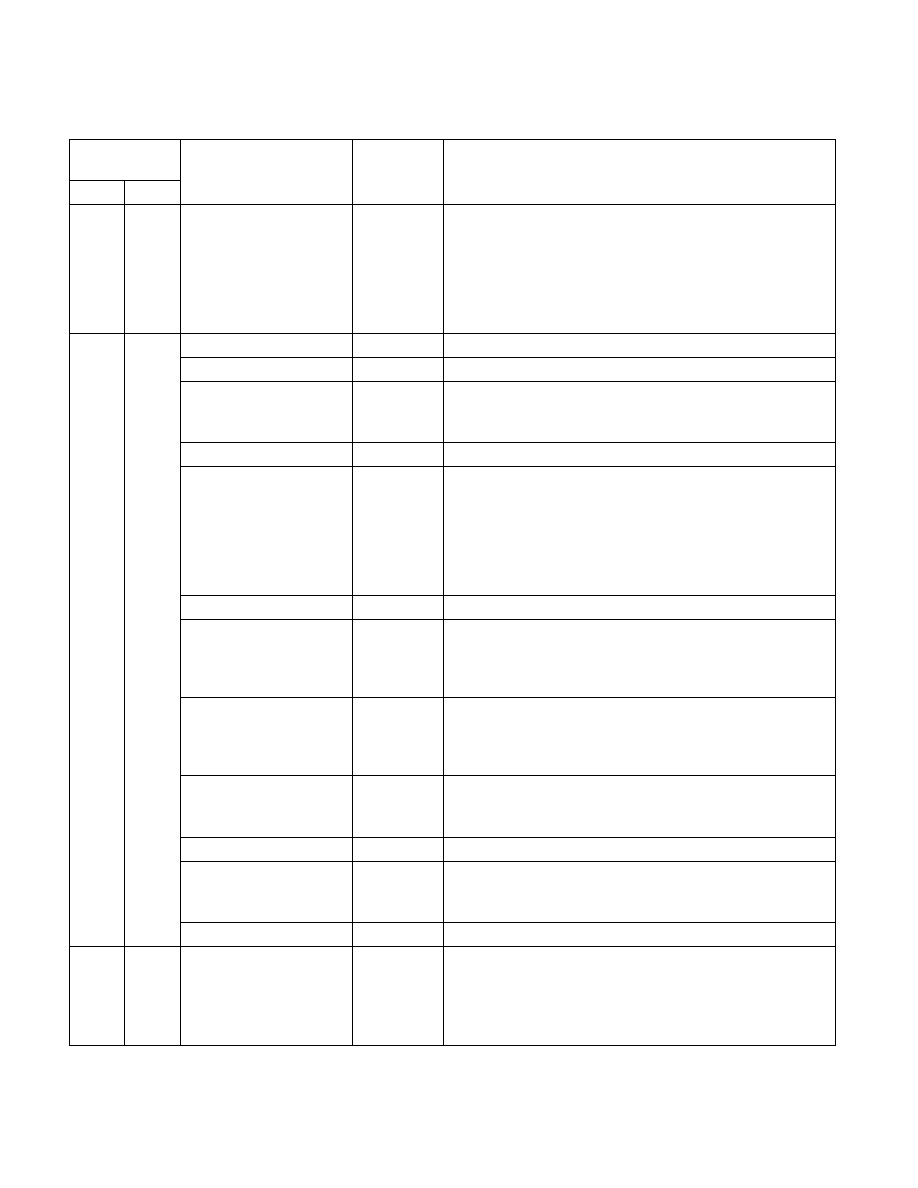

Vol. 3C 35-177

MODEL-SPECIFIC REGISTERS (MSRS)

63:0

Protected Processor Inventory Number (R/O)

A unique value within a given CPUID family/model/stepping

signature that a privileged inventory initialization agent can access

to identify each physical processor, when access to MSR_PPIN is

enabled. Access to MSR_PPIN is permitted only if

MSR_PPIN_CTL[bits 1:0] = ‘10b’

CEH

206

MSR_PLATFORM_INFO

Package

See http://biosbits.org.

7:0

Reserved.

15:8

Package

Maximum Non-Turbo Ratio (R/O)

The is the ratio of the frequency that invariant TSC runs at.

Frequency = ratio * 100 MHz.

22:16

Reserved.

23

Package

PPIN_CAP (R/O)

When set to 1, indicates that Protected Processor Inventory

Number (PPIN) capability can be enabled for privileged system

inventory agent to read PPIN from MSR_PPIN.

When set to 0, PPIN capability is not supported. An attempt to

access MSR_PPIN_CTL or MSR_PPIN will cause #GP.

27:24

Reserved.

28

Package

Programmable Ratio Limit for Turbo Mode (R/O)

When set to 1, indicates that Programmable Ratio Limits for Turbo

mode is enabled, and when set to 0, indicates Programmable Ratio

Limits for Turbo mode is disabled.

29

Package

Programmable TDP Limit for Turbo Mode (R/O)

When set to 1, indicates that TDP Limits for Turbo mode are

programmable, and when set to 0, indicates TDP Limit for Turbo

mode is not programmable.

30

Package

Programmable TJ OFFSET (R/O)

When set to 1, indicates that MSR_TEMPERATURE_TARGET.[27:24]

is valid and writable to specify an temperature offset.

39:31

Reserved.

47:40

Package

Maximum Efficiency Ratio (R/O)

The is the minimum ratio (maximum efficiency) that the processor

can operates, in units of 100MHz.

63:48

Reserved.

E2H

226

MSR_PKG_CST_CONFIG_

CONTROL

Core

C-State Configuration Control (R/W)

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-

States.

See http://biosbits.org.

Table 35-24. MSRs Supported by Intel® Xeon® Processors E5 v2 Product Family (based on Ivy Bridge-E

microarchitecture) (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec