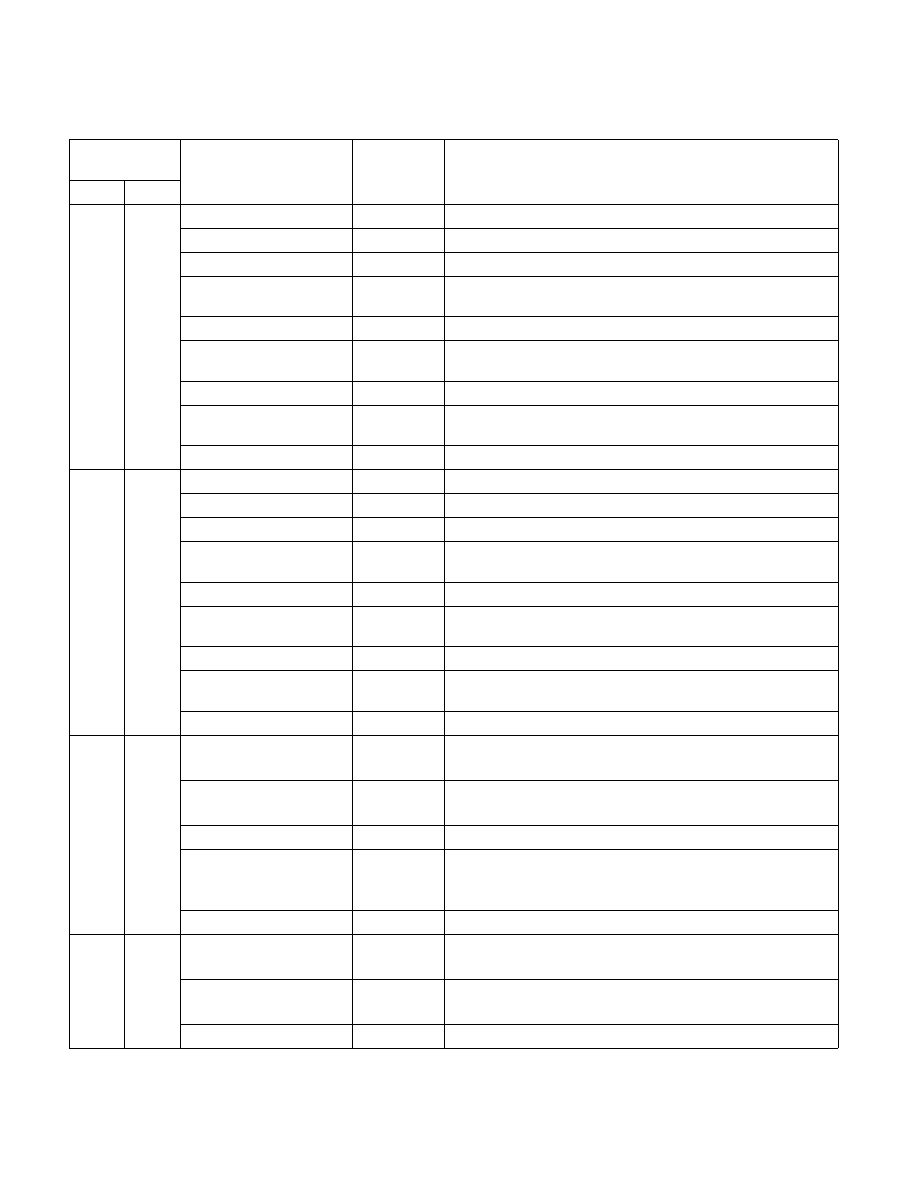

Vol. 3C 35-175

MODEL-SPECIFIC REGISTERS (MSRS)

649H

1609

MSR_CONFIG_TDP_LEVEL1

Package

ConfigTDP Level 1 ratio and power level (R/O)

14:0

PKG_TDP_LVL1. Power setting for ConfigTDP Level 1.

15

Reserved

23:16

Config_TDP_LVL1_Ratio. ConfigTDP level 1 ratio to be used for this

specific processor.

31:24

Reserved

46:32

PKG_MAX_PWR_LVL1. Max Power setting allowed for ConfigTDP

Level 1.

47

Reserved

62:48

PKG_MIN_PWR_LVL1. MIN Power setting allowed for ConfigTDP

Level 1.

63

Reserved.

64AH

1610

MSR_CONFIG_TDP_LEVEL2

Package

ConfigTDP Level 2 ratio and power level (R/O)

14:0

PKG_TDP_LVL2. Power setting for ConfigTDP Level 2.

15

Reserved

23:16

Config_TDP_LVL2_Ratio. ConfigTDP level 2 ratio to be used for this

specific processor.

31:24

Reserved

46:32

PKG_MAX_PWR_LVL2. Max Power setting allowed for ConfigTDP

Level 2.

47

Reserved

62:48

PKG_MIN_PWR_LVL2. MIN Power setting allowed for ConfigTDP

Level 2.

63

Reserved.

64BH

1611

MSR_CONFIG_TDP_

CONTROL

Package

ConfigTDP Control (R/W)

1:0

TDP_LEVEL (RW/L)

System BIOS can program this field.

30:2

Reserved.

31

Config_TDP_Lock (RW/L)

When this bit is set, the content of this register is locked until a

reset.

63:32

Reserved.

64CH

1612

MSR_TURBO_ACTIVATION_

RATIO

Package

ConfigTDP Control (R/W)

7:0

MAX_NON_TURBO_RATIO (RW/L)

System BIOS can program this field.

30:8

Reserved.

Table 35-23. Additional MSRs Supported by 3rd Generation Intel® Core™ Processors (based on Intel®

microarchitecture code name Ivy Bridge) (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec