35-170 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

C10H

MSR_U_PMON_EVNTSEL0

Package

Uncore U-box perfmon event select for U-box counter 0.

C11H

MSR_U_PMON_EVNTSEL1

Package

Uncore U-box perfmon event select for U-box counter 1.

C16H

MSR_U_PMON_CTR0

Package

Uncore U-box perfmon counter 0

C17H

MSR_U_PMON_CTR1

Package

Uncore U-box perfmon counter 1

C24H

MSR_PCU_PMON_BOX_CTL

Package

Uncore PCU perfmon for PCU-box-wide control

C30H

MSR_PCU_PMON_EVNTSEL0

Package

Uncore PCU perfmon event select for PCU counter 0.

C31H

MSR_PCU_PMON_EVNTSEL1

Package

Uncore PCU perfmon event select for PCU counter 1.

C32H

MSR_PCU_PMON_EVNTSEL2

Package

Uncore PCU perfmon event select for PCU counter 2.

C33H

MSR_PCU_PMON_EVNTSEL3

Package

Uncore PCU perfmon event select for PCU counter 3.

C34H

MSR_PCU_PMON_BOX_FILTER

Package

Uncore PCU perfmon box-wide filter.

C36H

MSR_PCU_PMON_CTR0

Package

Uncore PCU perfmon counter 0.

C37H

MSR_PCU_PMON_CTR1

Package

Uncore PCU perfmon counter 1.

C38H

MSR_PCU_PMON_CTR2

Package

Uncore PCU perfmon counter 2.

C39H

MSR_PCU_PMON_CTR3

Package

Uncore PCU perfmon counter 3.

D04H

MSR_C0_PMON_BOX_CTL

Package

Uncore C-box 0 perfmon local box wide control.

D10H

MSR_C0_PMON_EVNTSEL0

Package

Uncore C-box 0 perfmon event select for C-box 0 counter 0.

D11H

MSR_C0_PMON_EVNTSEL1

Package

Uncore C-box 0 perfmon event select for C-box 0 counter 1.

D12H

MSR_C0_PMON_EVNTSEL2

Package

Uncore C-box 0 perfmon event select for C-box 0 counter 2.

D13H

MSR_C0_PMON_EVNTSEL3

Package

Uncore C-box 0 perfmon event select for C-box 0 counter 3.

D14H

MSR_C0_PMON_BOX_FILTER

Package

Uncore C-box 0 perfmon box wide filter.

D16H

MSR_C0_PMON_CTR0

Package

Uncore C-box 0 perfmon counter 0.

D17H

MSR_C0_PMON_CTR1

Package

Uncore C-box 0 perfmon counter 1.

D18H

MSR_C0_PMON_CTR2

Package

Uncore C-box 0 perfmon counter 2.

D19H

MSR_C0_PMON_CTR3

Package

Uncore C-box 0 perfmon counter 3.

D24H

MSR_C1_PMON_BOX_CTL

Package

Uncore C-box 1 perfmon local box wide control.

D30H

MSR_C1_PMON_EVNTSEL0

Package

Uncore C-box 1 perfmon event select for C-box 1 counter 0.

D31H

MSR_C1_PMON_EVNTSEL1

Package

Uncore C-box 1 perfmon event select for C-box 1 counter 1.

D32H

MSR_C1_PMON_EVNTSEL2

Package

Uncore C-box 1 perfmon event select for C-box 1 counter 2.

D33H

MSR_C1_PMON_EVNTSEL3

Package

Uncore C-box 1 perfmon event select for C-box 1 counter 3.

D34H

MSR_C1_PMON_BOX_FILTER

Package

Uncore C-box 1 perfmon box wide filter.

D36H

MSR_C1_PMON_CTR0

Package

Uncore C-box 1 perfmon counter 0.

D37H

MSR_C1_PMON_CTR1

Package

Uncore C-box 1 perfmon counter 1.

D38H

MSR_C1_PMON_CTR2

Package

Uncore C-box 1 perfmon counter 2.

D39H

MSR_C1_PMON_CTR3

Package

Uncore C-box 1 perfmon counter 3.

D44H

MSR_C2_PMON_BOX_CTL

Package

Uncore C-box 2 perfmon local box wide control.

D50H

MSR_C2_PMON_EVNTSEL0

Package

Uncore C-box 2 perfmon event select for C-box 2 counter 0.

D51H

MSR_C2_PMON_EVNTSEL1

Package

Uncore C-box 2 perfmon event select for C-box 2 counter 1.

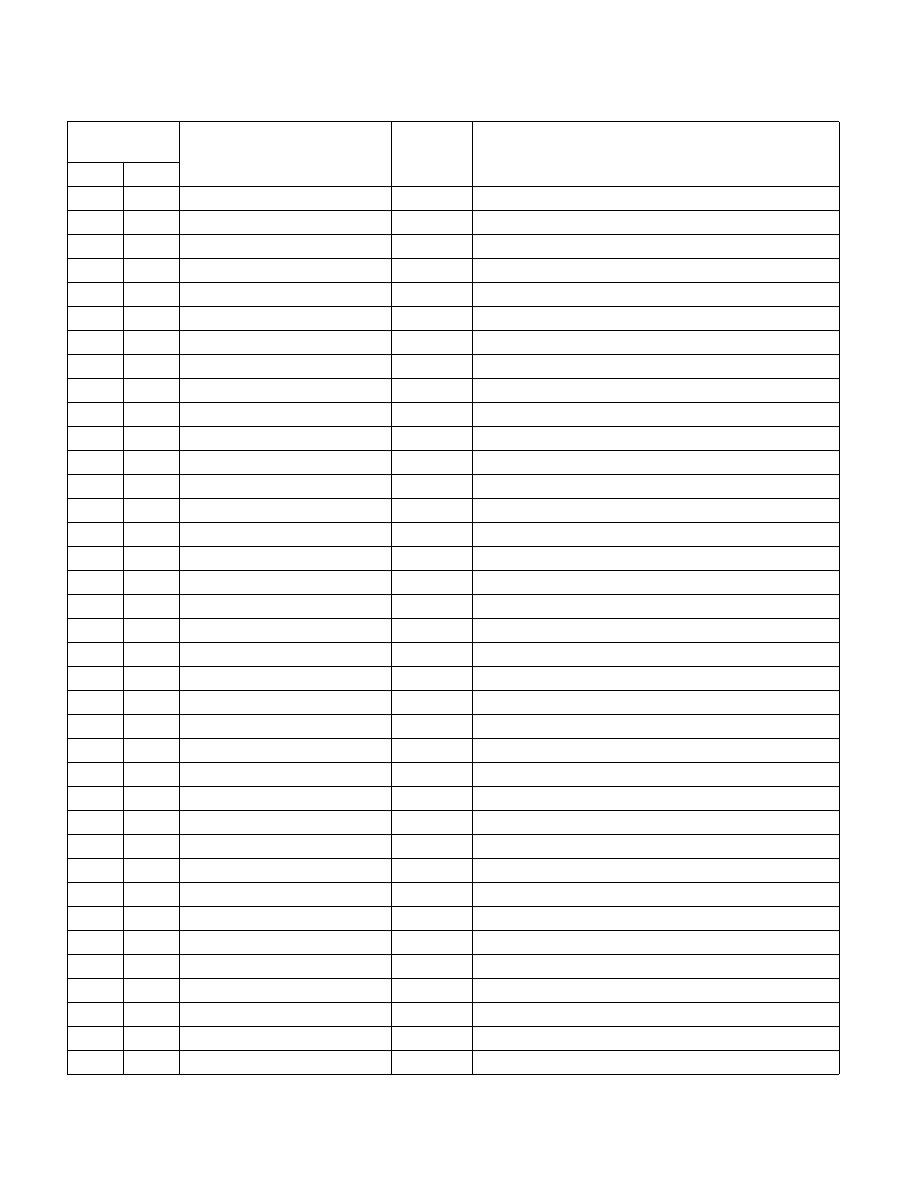

Table 35-22. Uncore PMU MSRs in Intel® Xeon® Processor E5 Family (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec