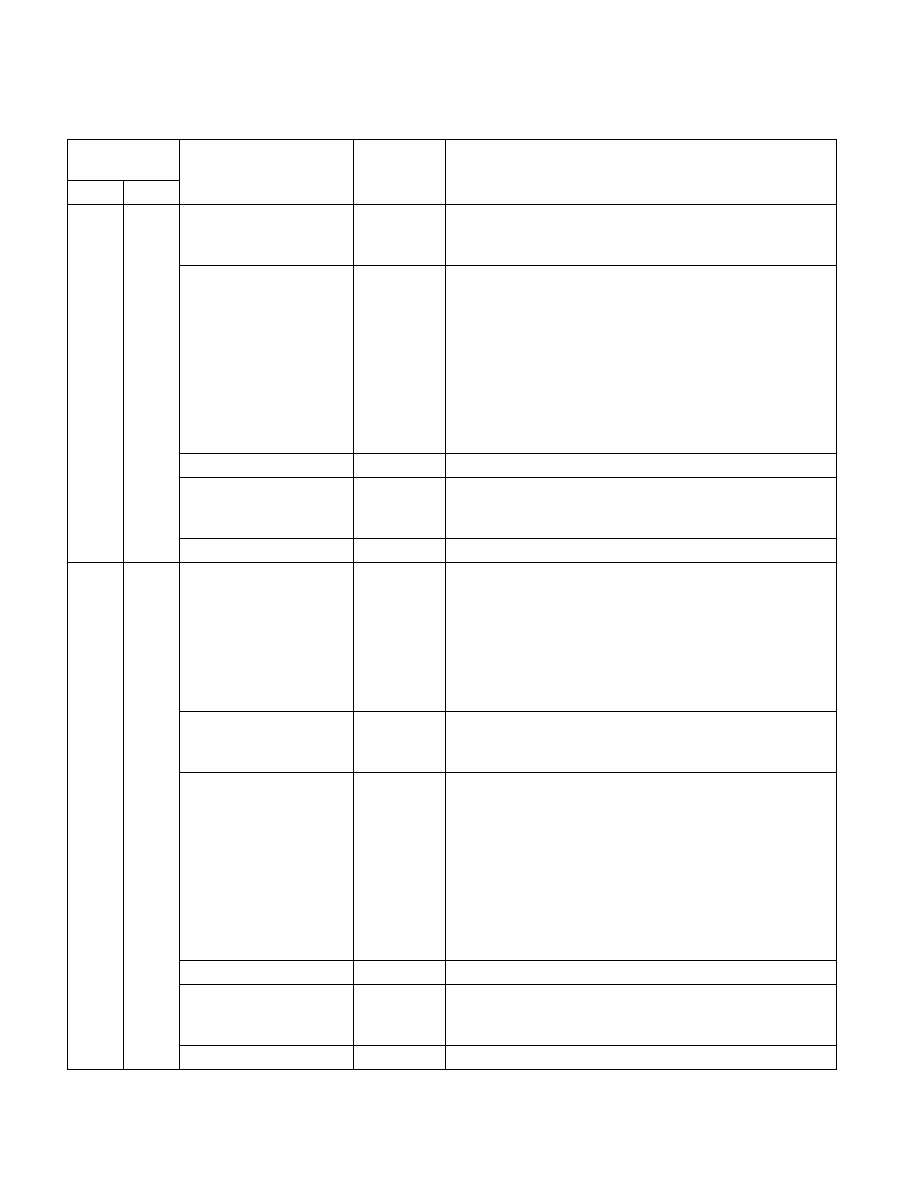

35-158 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

9:0

Interrupt response time limit (R/W)

Specifies the limit that should be used to decide if the package

should be put into a package C3 state.

12:10

Time Unit (R/W)

Specifies the encoding value of time unit of the interrupt response

time limit. The following time unit encodings are supported:

000b: 1 ns

001b: 32 ns

010b: 1024 ns

011b: 32768 ns

100b: 1048576 ns

101b: 33554432 ns

14:13

Reserved.

15

Valid (R/W)

Indicates whether the values in bits 12:0 are valid and can be used

by the processor for package C-sate management.

63:16

Reserved.

60BH

1547

MSR_PKGC6_IRTL

Package

Package C6 Interrupt Response Limit (R/W)

This MSR defines the budget allocated for the package to exit from

C6 to a C0 state, where interrupt request can be delivered to the

core and serviced. Additional core-exit latency amy be applicable

depending on the actual C-state the core is in.

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-

States.

9:0

Interrupt response time limit (R/W)

Specifies the limit that should be used to decide if the package

should be put into a package C6 state.

12:10

Time Unit (R/W)

Specifies the encoding value of time unit of the interrupt response

time limit. The following time unit encodings are supported:

000b: 1 ns

001b: 32 ns

010b: 1024 ns

011b: 32768 ns

100b: 1048576 ns

101b: 33554432 ns

14:13

Reserved.

15

Valid (R/W)

Indicates whether the values in bits 12:0 are valid and can be used

by the processor for package C-sate management.

63:16

Reserved.

Table 35-18. MSRs Supported by Intel® Processors

based on Intel® microarchitecture code name Sandy Bridge (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec