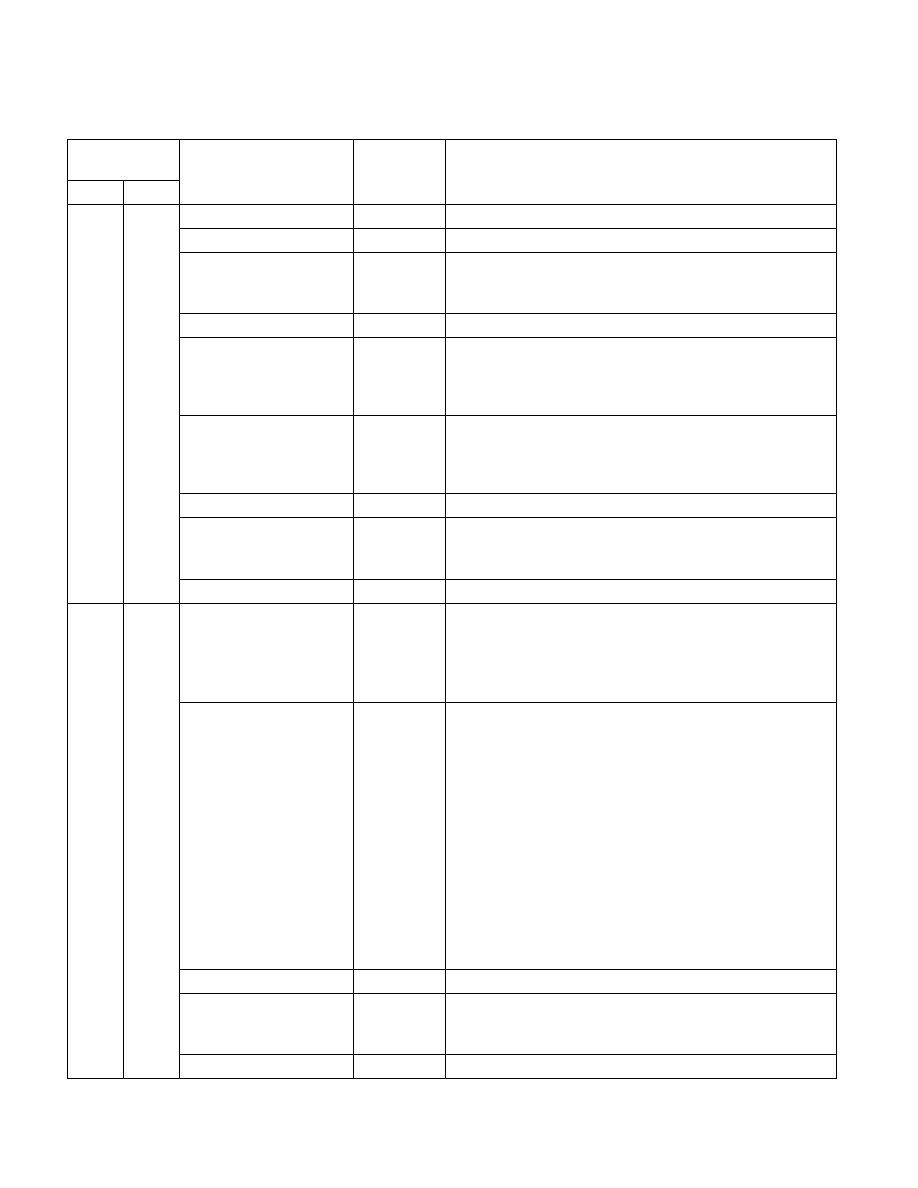

35-144 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

CEH

206

MSR_PLATFORM_INFO

Package

See http://biosbits.org.

7:0

Reserved.

15:8

Package

Maximum Non-Turbo Ratio (R/O)

The is the ratio of the frequency that invariant TSC runs at.

Frequency = ratio * 100 MHz.

27:16

Reserved.

28

Package

Programmable Ratio Limit for Turbo Mode (R/O)

When set to 1, indicates that Programmable Ratio Limits for Turbo

mode is enabled, and when set to 0, indicates Programmable Ratio

Limits for Turbo mode is disabled.

29

Package

Programmable TDP Limit for Turbo Mode (R/O)

When set to 1, indicates that TDP Limits for Turbo mode are

programmable, and when set to 0, indicates TDP Limit for Turbo

mode is not programmable.

39:30

Reserved.

47:40

Package

Maximum Efficiency Ratio (R/O)

The is the minimum ratio (maximum efficiency) that the processor

can operates, in units of 100MHz.

63:48

Reserved.

E2H

226

MSR_PKG_CST_CONFIG_

CONTROL

Core

C-State Configuration Control (R/W)

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-

States.

See http://biosbits.org.

2:0

Package C-State Limit (R/W)

Specifies the lowest processor-specific C-state code name

(consuming the least power). for the package. The default is set as

factory-configured package C-state limit.

The following C-state code name encodings are supported:

000b: C0/C1 (no package C-sate support)

001b: C2

010b: C6 no retention

011b: C6 retention

100b: C7

101b: C7s

111: No package C-state limit.

Note: This field cannot be used to limit package C-state to C3.

9:3

Reserved.

10

I/O MWAIT Redirection Enable (R/W)

When set, will map IO_read instructions sent to IO register

specified by MSR_PMG_IO_CAPTURE_BASE to MWAIT instructions

14:11

Reserved.

Table 35-18. MSRs Supported by Intel® Processors

based on Intel® microarchitecture code name Sandy Bridge (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec