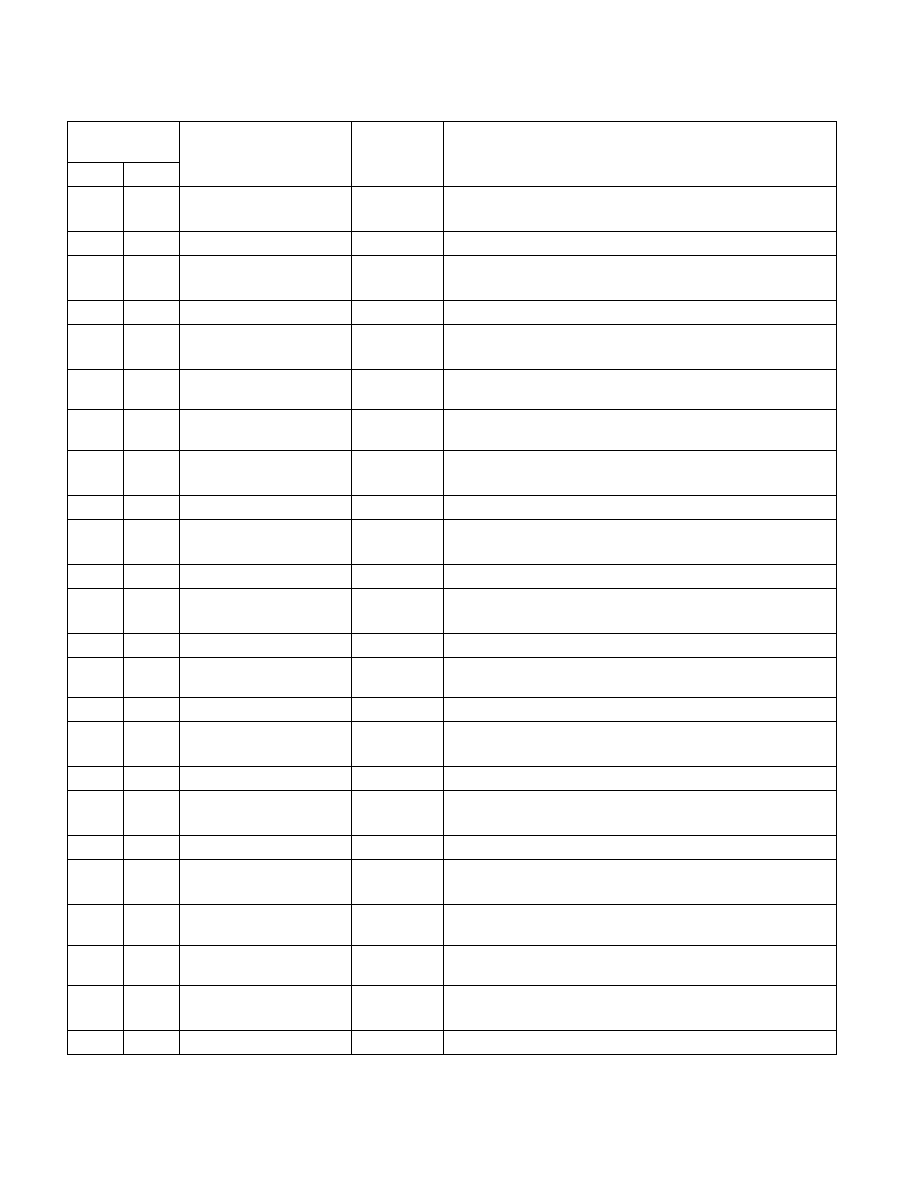

35-132 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

CF8H

3320

MSR_M1_PMON_EVNT_

SEL4

Package

Uncore M-box 1 perfmon event select MSR.

CF9H

3321

MSR_M1_PMON_CTR4

Package

Uncore M-box 1 perfmon counter MSR.

CFAH

3322

MSR_M1_PMON_EVNT_

SEL5

Package

Uncore M-box 1 perfmon event select MSR.

CFBH

3323

MSR_M1_PMON_CTR5

Package

Uncore M-box 1 perfmon counter MSR.

D00H

3328

MSR_C0_PMON_BOX_CTRL Package

Uncore C-box 0 perfmon local box control MSR.

D01H

3329

MSR_C0_PMON_BOX_

STATUS

Package

Uncore C-box 0 perfmon local box status MSR.

D02H

3330

MSR_C0_PMON_BOX_OVF_

CTRL

Package

Uncore C-box 0 perfmon local box overflow control MSR.

D10H

3344

MSR_C0_PMON_EVNT_

SEL0

Package

Uncore C-box 0 perfmon event select MSR.

D11H

3345

MSR_C0_PMON_CTR0

Package

Uncore C-box 0 perfmon counter MSR.

D12H

3346

MSR_C0_PMON_EVNT_

SEL1

Package

Uncore C-box 0 perfmon event select MSR.

D13H

3347

MSR_C0_PMON_CTR1

Package

Uncore C-box 0 perfmon counter MSR.

D14H

3348

MSR_C0_PMON_EVNT_

SEL2

Package

Uncore C-box 0 perfmon event select MSR.

D15H

3349

MSR_C0_PMON_CTR2

Package

Uncore C-box 0 perfmon counter MSR.

D16H

3350

MSR_C0_PMON_EVNT_

SEL3

Package

Uncore C-box 0 perfmon event select MSR.

D17H

3351

MSR_C0_PMON_CTR3

Package

Uncore C-box 0 perfmon counter MSR.

D18H

3352

MSR_C0_PMON_EVNT_

SEL4

Package

Uncore C-box 0 perfmon event select MSR.

D19H

3353

MSR_C0_PMON_CTR4

Package

Uncore C-box 0 perfmon counter MSR.

D1AH

3354

MSR_C0_PMON_EVNT_

SEL5

Package

Uncore C-box 0 perfmon event select MSR.

D1BH

3355

MSR_C0_PMON_CTR5

Package

Uncore C-box 0 perfmon counter MSR.

D20H

3360

MSR_C4_PMON_BOX_CTRL Package

Uncore C-box 4 perfmon local box control MSR.

D21H

3361

MSR_C4_PMON_BOX_

STATUS

Package

Uncore C-box 4 perfmon local box status MSR.

D22H

3362

MSR_C4_PMON_BOX_OVF_

CTRL

Package

Uncore C-box 4 perfmon local box overflow control MSR.

D30H

3376

MSR_C4_PMON_EVNT_

SEL0

Package

Uncore C-box 4 perfmon event select MSR.

D31H

3377

MSR_C4_PMON_CTR0

Package

Uncore C-box 4 perfmon counter MSR.

Table 35-15. Additional MSRs in Intel® Xeon® Processor 7500 Series (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec