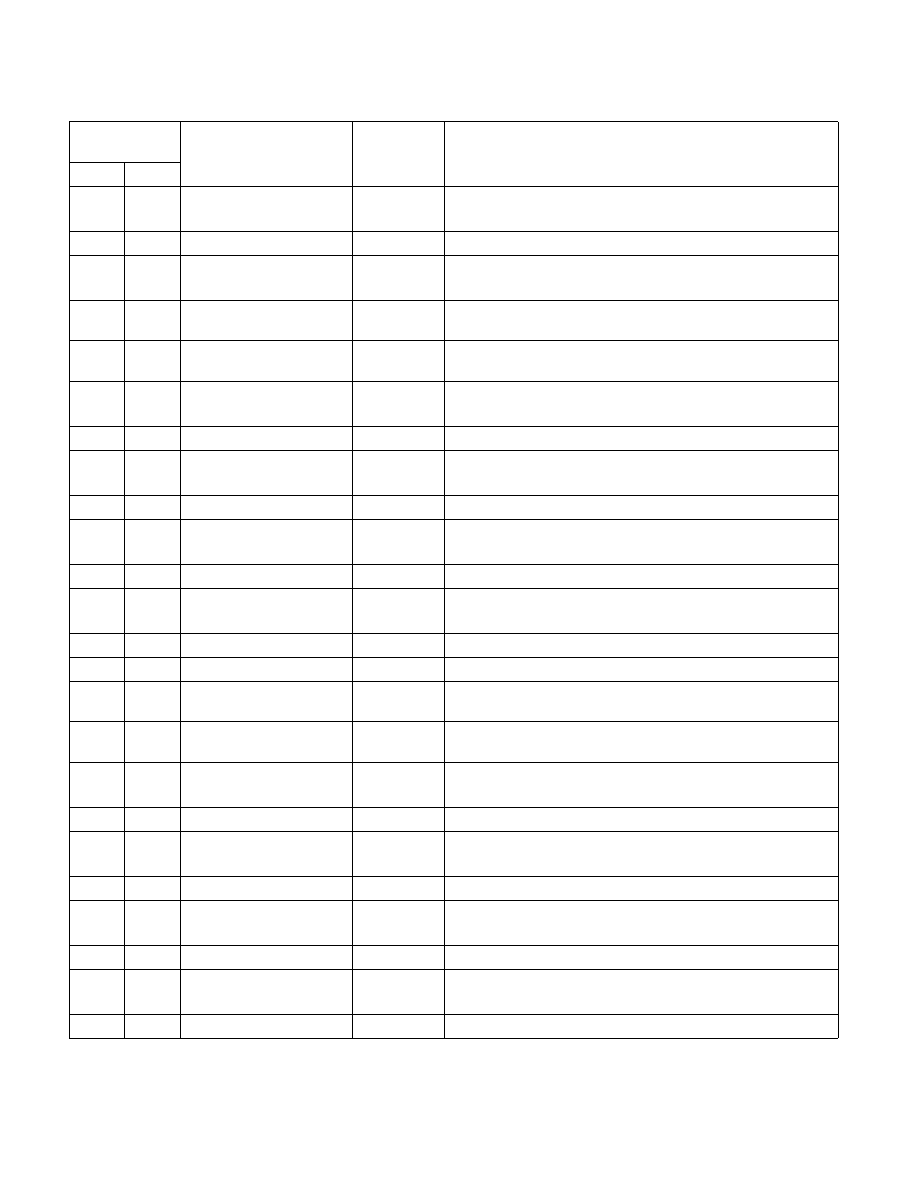

Vol. 3C 35-129

MODEL-SPECIFIC REGISTERS (MSRS)

C56H

3158

MSR_S0_PMON_EVNT_

SEL3

Package

Uncore S-box 0 perfmon event select MSR.

C57H

3159

MSR_S0_PMON_CTR3

Package

Uncore S-box 0 perfmon counter MSR.

C60H

3168

MSR_B1_PMON_BOX_CTRL Package

Uncore B-box 1 perfmon local box control MSR.

C61H

3169

MSR_B1_PMON_BOX_

STATUS

Package

Uncore B-box 1 perfmon local box status MSR.

C62H

3170

MSR_B1_PMON_BOX_OVF_

CTRL

Package

Uncore B-box 1 perfmon local box overflow control MSR.

C70H

3184

MSR_B1_PMON_EVNT_

SEL0

Package

Uncore B-box 1 perfmon event select MSR.

C71H

3185

MSR_B1_PMON_CTR0

Package

Uncore B-box 1 perfmon counter MSR.

C72H

3186

MSR_B1_PMON_EVNT_

SEL1

Package

Uncore B-box 1 perfmon event select MSR.

C73H

3187

MSR_B1_PMON_CTR1

Package

Uncore B-box 1 perfmon counter MSR.

C74H

3188

MSR_B1_PMON_EVNT_

SEL2

Package

Uncore B-box 1 perfmon event select MSR.

C75H

3189

MSR_B1_PMON_CTR2

Package

Uncore B-box 1 perfmon counter MSR.

C76H

3190

MSR_B1_PMON_EVNT_

SEL3

Package

Uncore B-box 1vperfmon event select MSR.

C77H

3191

MSR_B1_PMON_CTR3

Package

Uncore B-box 1 perfmon counter MSR.

C80H

3120

MSR_W_PMON_BOX_CTRL

Package

Uncore W-box perfmon local box control MSR.

C81H

3121

MSR_W_PMON_BOX_

STATUS

Package

Uncore W-box perfmon local box status MSR.

C82H

3122

MSR_W_PMON_BOX_OVF_

CTRL

Package

Uncore W-box perfmon local box overflow control MSR.

C90H

3136

MSR_W_PMON_EVNT_SEL0 Package

Uncore W-box perfmon event select MSR.

C91H

3137

MSR_W_PMON_CTR0

Package

Uncore W-box perfmon counter MSR.

C92H

3138

MSR_W_PMON_EVNT_SEL1 Package

Uncore W-box perfmon event select MSR.

C93H

3139

MSR_W_PMON_CTR1

Package

Uncore W-box perfmon counter MSR.

C94H

3140

MSR_W_PMON_EVNT_SEL2 Package

Uncore W-box perfmon event select MSR.

C95H

3141

MSR_W_PMON_CTR2

Package

Uncore W-box perfmon counter MSR.

C96H

3142

MSR_W_PMON_EVNT_SEL3 Package

Uncore W-box perfmon event select MSR.

C97H

3143

MSR_W_PMON_CTR3

Package

Uncore W-box perfmon counter MSR.

Table 35-15. Additional MSRs in Intel® Xeon® Processor 7500 Series (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec