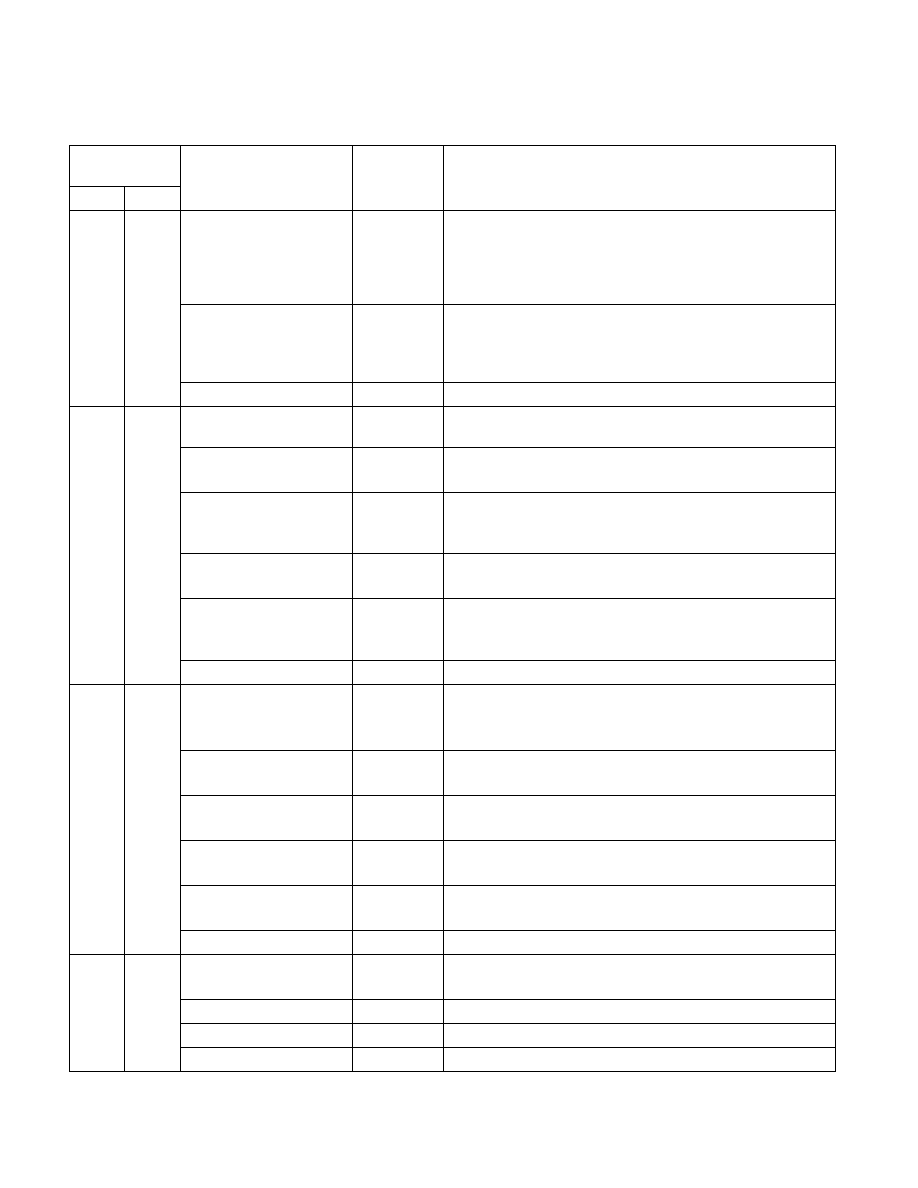

Vol. 3C 35-113

MODEL-SPECIFIC REGISTERS (MSRS)

0

Package

EIST Hardware Coordination Disable (R/W)

When 0, enables hardware coordination of Enhanced Intel

Speedstep Technology request from processor cores; When 1,

disables hardware coordination of Enhanced Intel Speedstep

Technology requests.

1

Thread

Energy/Performance Bias Enable (R/W)

This bit makes the IA32_ENERGY_PERF_BIAS register (MSR 1B0h)

visible to software with Ring 0 privileges. This bit’s status (1 or 0)

is also reflected by CPUID.(EAX=06h):ECX[3].

63:2

Reserved.

1ACH

428

MSR_TURBO_POWER_

CURRENT_LIMIT

See http://biosbits.org.

14:0

Package

TDP Limit (R/W)

TDP limit in 1/8 Watt granularity.

15

Package

TDP Limit Override Enable (R/W)

A value = 0 indicates override is not active, and a value = 1

indicates active.

30:16

Package

TDC Limit (R/W)

TDC limit in 1/8 Amp granularity.

31

Package

TDC Limit Override Enable (R/W)

A value = 0 indicates override is not active, and a value = 1

indicates active.

63:32

Reserved.

1ADH

429

MSR_TURBO_RATIO_LIMIT

Package

Maximum Ratio Limit of Turbo Mode

RO if MSR_PLATFORM_INFO.[28] = 0,

RW if MSR_PLATFORM_INFO.[28] = 1

7:0

Package

Maximum Ratio Limit for 1C

Maximum turbo ratio limit of 1 core active.

15:8

Package

Maximum Ratio Limit for 2C

Maximum turbo ratio limit of 2 core active.

23:16

Package

Maximum Ratio Limit for 3C

Maximum turbo ratio limit of 3 core active.

31:24

Package

Maximum Ratio Limit for 4C

Maximum turbo ratio limit of 4 core active.

63:32

Reserved.

1C8H

456

MSR_LBR_SELECT

Core

Last Branch Record Filtering Select Register (R/W)

See Section 17.7.2, “Filtering of Last Branch Records.”

0

CPL_EQ_0

1

CPL_NEQ_0

2

JCC

Table 35-13. MSRs in Processors Based on Intel® Microarchitecture Code Name Nehalem (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec