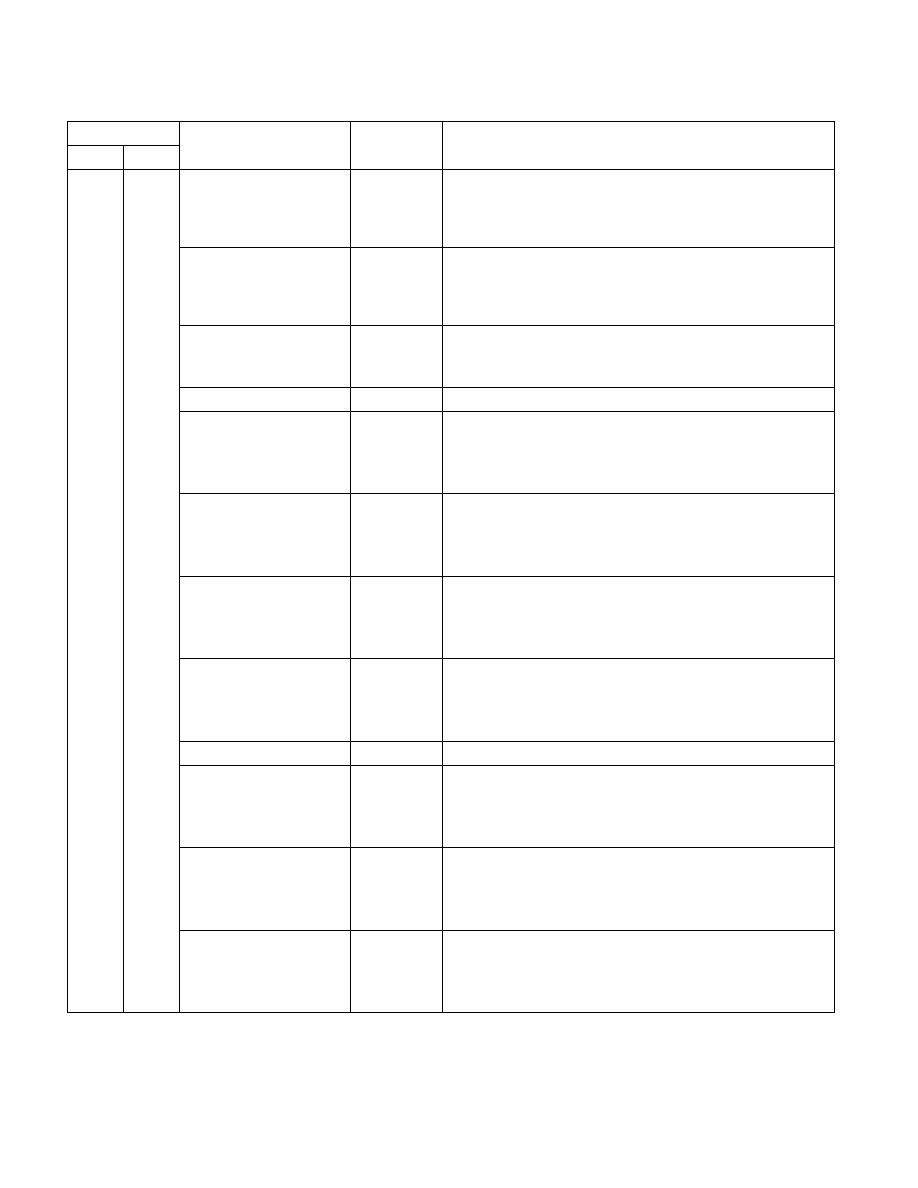

35-100 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

12

Electrical Design Point Status (R0)

When set, frequency is reduced below the operating system

request due to electrical design point constraints (e.g. maximum

electrical current consumption).

13

Turbo Transition Attenuation Status (R0)

When set, frequency is reduced below the operating system

request due to Turbo transition attenuation. This prevents

performance degradation due to frequent operating ratio changes.

14

Maximum Efficiency Frequency Status (R0)

When set, frequency is reduced below the maximum efficiency

frequency.

15

Reserved

16

PROCHOT Log

When set, indicates that the PROCHOT Status bit has asserted

since the log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

17

Thermal Log

When set, indicates that the Thermal Status bit has asserted since

the log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

18

Package-Level PL1 Power Limiting Log

When set, indicates that the Package Level PL1 Power Limiting

Status bit has asserted since the log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

19

Package-Level PL2 Power Limiting Log

When set, indicates that the Package Level PL2 Power Limiting

Status bit has asserted since the log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

24:20

Reserved.

25

Core Power Limiting Log

When set, indicates that the Core Power Limiting Status bit has

asserted since the log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

26

VR Therm Alert Log

When set, indicates that the VR Therm Alert Status bit has

asserted since the log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

27

Max Turbo Limit Log

When set, indicates that the Max Turbo Limit Status bit has

asserted since the log bit was last cleared.

This log bit will remain set until cleared by software writing 0.

Table 35-12. MSRs in Next Generation Intel Atom Processors Based on the Goldmont Microarchitecture (Contd.)

Address

Register Name

Scope

Bit Description

Hex

Dec