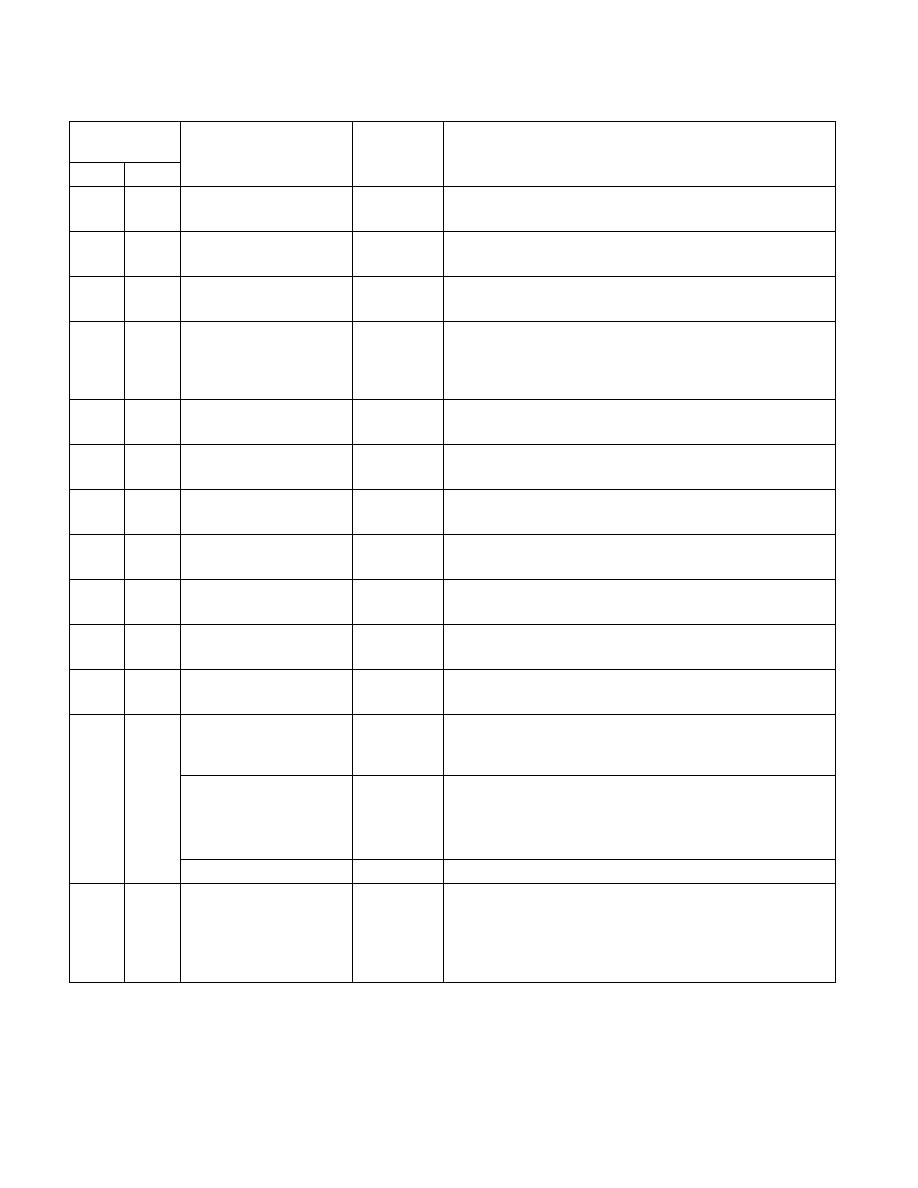

Vol. 3C 35-77

MODEL-SPECIFIC REGISTERS (MSRS)

45H

69

MSR_

LASTBRANCH_5_FROM_IP

Core

Last Branch Record 5 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

46H

70

MSR_

LASTBRANCH_6_FROM_IP

Core

Last Branch Record 6 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

47H

71

MSR_

LASTBRANCH_7_FROM_IP

Core

Last Branch Record 7 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

60H

96

MSR_

LASTBRANCH_0_TO_IP

Core

Last Branch Record 0 To IP (R/W)

One of eight pairs of last branch record registers on the last branch

record stack. The To_IP part of the stack contains pointers to the

destination instruction.

61H

97

MSR_

LASTBRANCH_1_TO_IP

Core

Last Branch Record 1 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

62H

98

MSR_

LASTBRANCH_2_TO_IP

Core

Last Branch Record 2 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

63H

99

MSR_

LASTBRANCH_3_TO_IP

Core

Last Branch Record 3 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

64H

100

MSR_

LASTBRANCH_4_TO_IP

Core

Last Branch Record 4 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

65H

101

MSR_

LASTBRANCH_5_TO_IP

Core

Last Branch Record 5 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

66H

102

MSR_

LASTBRANCH_6_TO_IP

Core

Last Branch Record 6 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

67H

103

MSR_

LASTBRANCH_7_TO_IP

Core

Last Branch Record 7 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

CDH

205

MSR_FSB_FREQ

Module

Scaleable Bus Speed(RO)

This field indicates the intended scaleable bus clock speed for

processors based on Silvermont microarchitecture:

2:0

• 100B: 080.0 MHz

• 000B: 083.3 MHz

• 001B: 100.0 MHz

• 010B: 133.3 MHz

• 011B: 116.7 MHz

63:3

Reserved.

E2H

226

MSR_PKG_CST_CONFIG_

CONTROL

Module

C-State Configuration Control (R/W)

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-

States.

See http://biosbits.org.

Table 35-7. MSRs Common to the Silvermont and Airmont Microarchitectures

Register

Address

Register Name

Scope

Bit Description

Hex

Dec