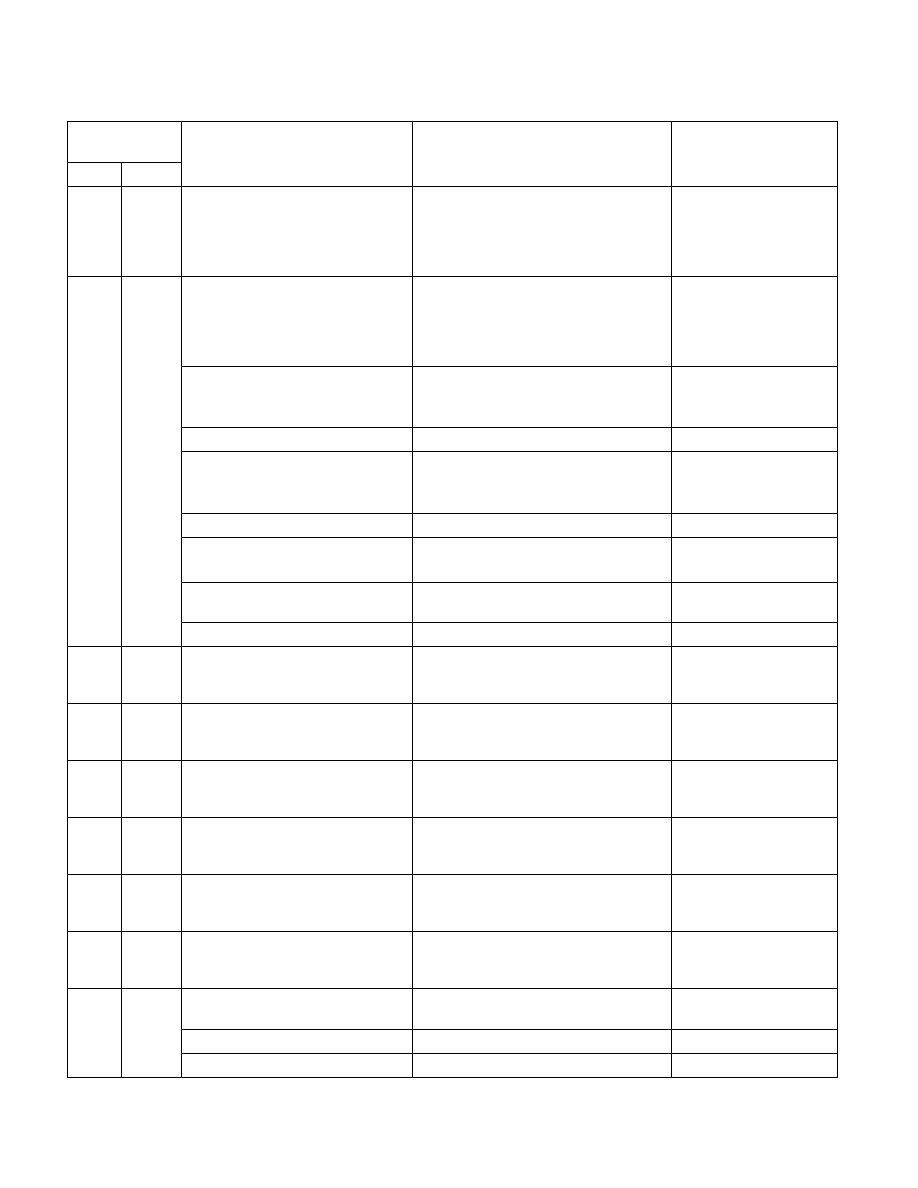

35-42 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

4000_

0000H

-

4000_

00FFH

Reserved MSR Address Space

All existing and future processors will

not implement MSR in this range.

C000_

0080H

IA32_EFER

Extended Feature Enables

If (

CPUID.80000001H:EDX.[2

0] ||

CPUID.80000001H:EDX.[2

9])

0

SYSCALL Enable: IA32_EFER.SCE (R/W)

Enables SYSCALL/SYSRET instructions in

64-bit mode.

7:1

Reserved.

8

IA-32e Mode Enable: IA32_EFER.LME

(R/W)

Enables IA-32e mode operation.

9

Reserved.

10

IA-32e Mode Active: IA32_EFER.LMA (R)

Indicates IA-32e mode is active when set.

11

Execute Disable Bit Enable:

IA32_EFER.NXE (R/W)

63:12

Reserved.

C000_

0081H

IA32_STAR

System Call Target Address (R/W)

If

CPUID.80000001:EDX.[29]

= 1

C000_

0082H

IA32_LSTAR

IA-32e Mode System Call Target Address

(R/W)

If

CPUID.80000001:EDX.[29]

= 1

C000_

0084H

IA32_FMASK

System Call Flag Mask (R/W)

If

CPUID.80000001:EDX.[29]

= 1

C000_

0100H

IA32_FS_BASE

Map of BASE Address of FS (R/W)

If

CPUID.80000001:EDX.[29]

= 1

C000_

0101H

IA32_GS_BASE

Map of BASE Address of GS (R/W)

If

CPUID.80000001:EDX.[29]

= 1

C000_

0102H

IA32_KERNEL_GS_BASE

Swap Target of BASE Address of GS

(R/W)

If

CPUID.80000001:EDX.[29]

= 1

C000_

0103H

IA32_TSC_AUX

Auxiliary TSC (RW)

If CPUID.80000001H:

EDX[27] = 1

31:0

AUX: Auxiliary signature of TSC

63:32

Reserved.

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal