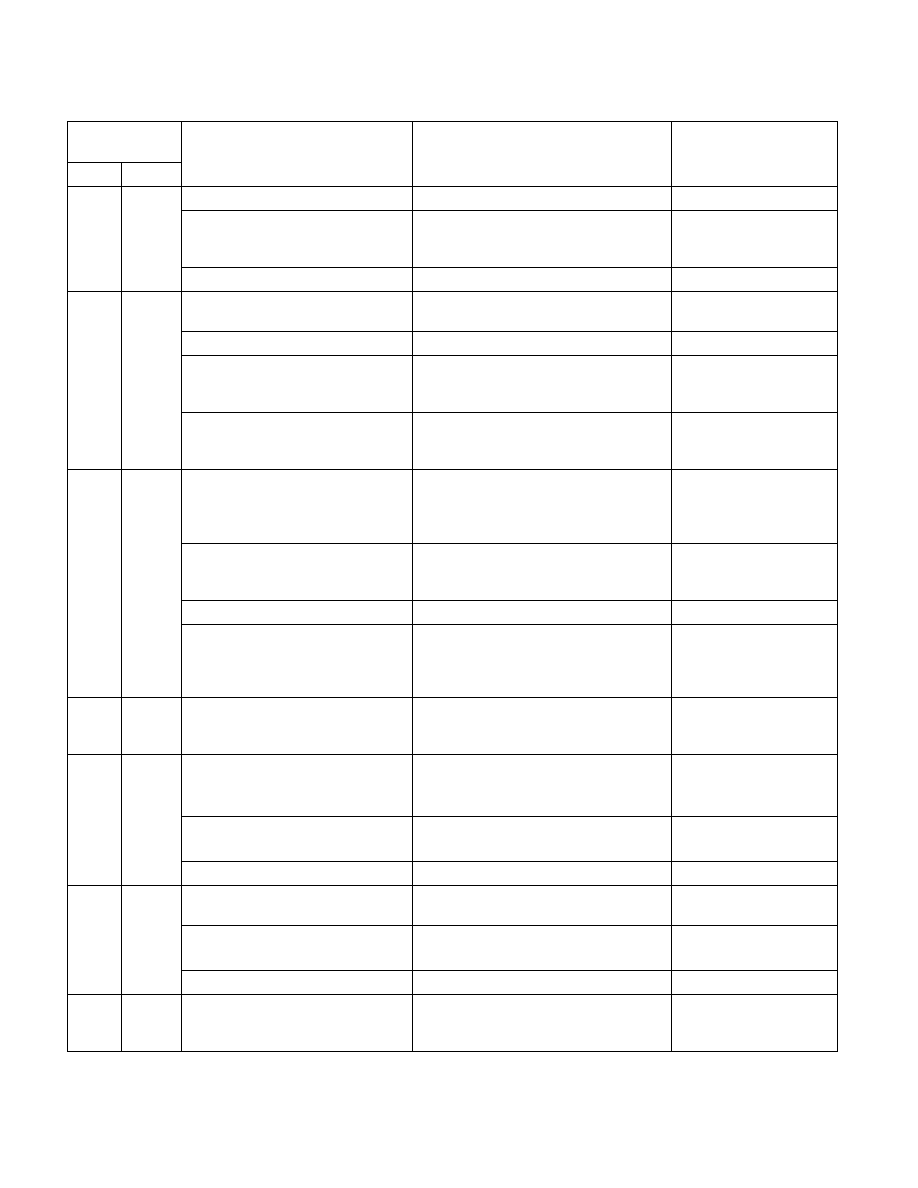

35-40 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

31: 8

Reserved.

N+31:32

Resource Monitoring ID: ID for monitoring

hardware to report monitored data via

IA32_QM_CTR.

N = Ceil (Log

2

(

CPUID.(EAX= 0FH,

ECX=0H).EBX[31:0] +1))

63:N+32

Reserved.

C8EH

3214

IA32_QM_CTR

Monitoring Counter Register (R/O)

If ( CPUID.(EAX=07H,

ECX=0):EBX.[12] = 1 )

61:0

Resource Monitored Data

62

Unavailable: If 1, indicates data for this

RMID is not available or not monitored for

this resource or RMID.

63

Error: If 1, indicates and unsupported RMID

or event type was written to

IA32_PQR_QM_EVTSEL.

C8FH

3215

IA32_PQR_ASSOC

Resource Association Register (R/W)

If ( (CPUID.(EAX=07H,

ECX=0):EBX[12] =1) or

(CPUID.(EAX=07H,

ECX=0):EBX[15] =1 ) )

N-1:0

Resource Monitoring ID (R/W): ID for

monitoring hardware to track internal

operation, e.g. memory access.

N = Ceil (Log

2

(

CPUID.(EAX= 0FH,

ECX=0H).EBX[31:0] +1))

31:N

Reserved

63:32

COS (R/W).

The class of service

(COS) to enforce (on writes);

returns the current COS when

read.

If ( CPUID.(EAX=07H,

ECX=0):EBX.[15] = 1 )

C90H -

D8FH

Reserved MSR Address Space for CAT

Mask Registers

See Section 17.17.3.1, “Enumeration and

Detection Support of Cache Allocation

C90H

3216

IA32_L3_MASK_0

L3 CAT Mask for COS0 (R/W)

If (CPUID.(EAX=10H,

ECX=0H):EBX[1] != 0)

31:0

Capacity Bit Mask (R/W)

63:32

Reserved.

C90H+

n

3216+n IA32_L3_MASK_n

L3 CAT Mask for COSn (R/W)

n = CPUID.(EAX=10H,

ECX=1H):EDX[15:0]

31:0

Capacity Bit Mask (R/W)

63:32

Reserved.

D10H -

D4FH

Reserved MSR Address Space for L2

CAT Mask Registers

See Section 17.17.3.1, “Enumeration and

Detection Support of Cache Allocation

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal