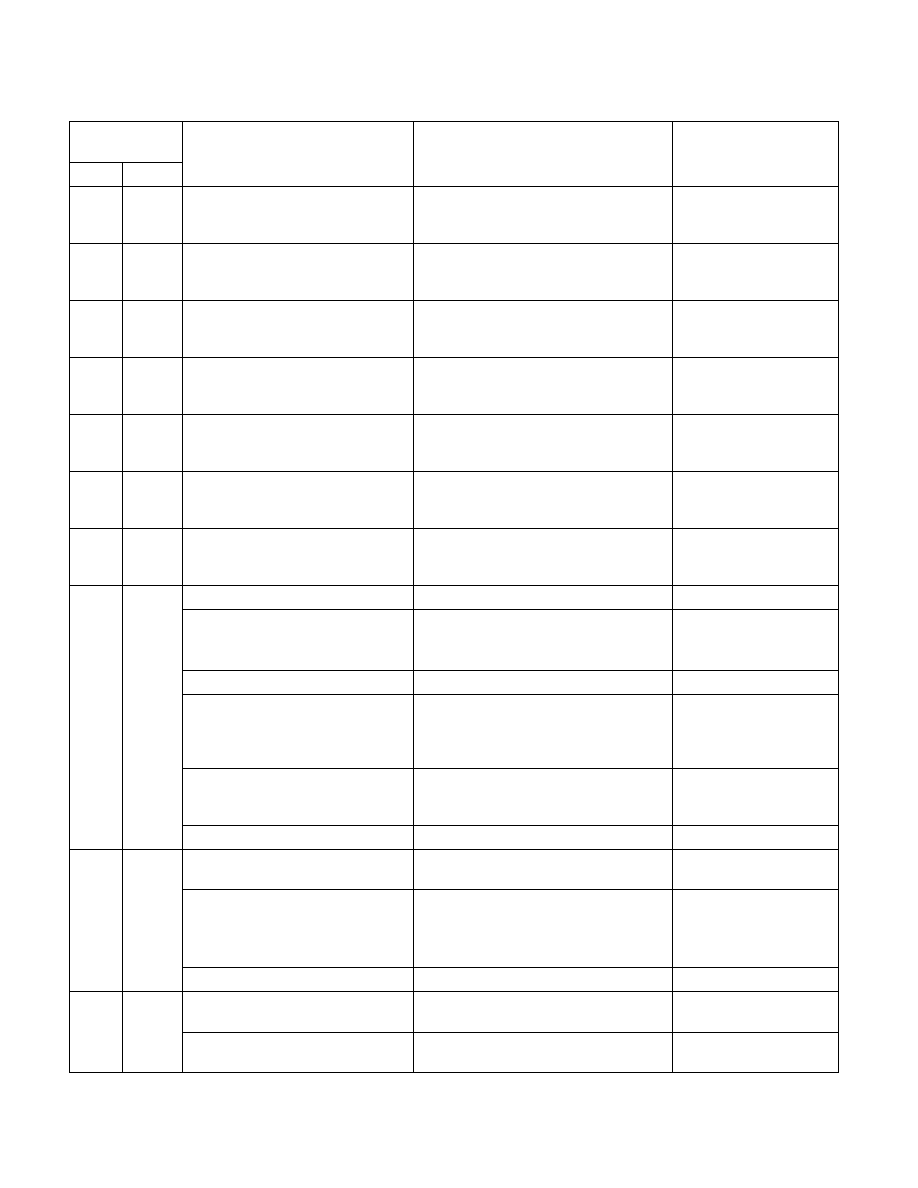

Vol. 3C 35-39

MODEL-SPECIFIC REGISTERS (MSRS)

835H

2101

IA32_X2APIC_LVT_LINT0

x2APIC LVT LINT0 Register (R/W)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

836H

2102

IA32_X2APIC_LVT_LINT1

x2APIC LVT LINT1 Register (R/W)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

837H

2103

IA32_X2APIC_LVT_ERROR

x2APIC LVT Error Register (R/W)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

838H

2104

IA32_X2APIC_INIT_COUNT

x2APIC Initial Count Register (R/W)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

839H

2105

IA32_X2APIC_CUR_COUNT

x2APIC Current Count Register (R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

83EH

2110

IA32_X2APIC_DIV_CONF

x2APIC Divide Configuration Register

(R/W)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

83FH

2111

IA32_X2APIC_SELF_IPI

x2APIC Self IPI Register (W/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

C80H

3200

IA32_DEBUG_INTERFACE

Silicon Debug Feature Control (R/W)

If CPUID.01H:ECX.[11] = 1

0

Enable (R/W)

BIOS set 1 to enable Silicon debug features.

Default is 0

If CPUID.01H:ECX.[11] = 1

29:1

Reserved.

30

Lock (R/W): If 1, locks any further change

to the MSR. The lock bit is set automatically

on the first SMI assertion even if not

explicitly set by BIOS. Default is 0.

If CPUID.01H:ECX.[11] = 1

31

Debug Occurred (R/O): This “sticky bit” is

set by hardware to indicate the status of

bit 0. Default is 0.

If CPUID.01H:ECX.[11] = 1

63:32

Reserved.

C81H

3201

IA32_L3_QOS_CFG

L3 QOS Configuration (R/W)

If ( CPUID.(EAX=10H,

ECX=1):ECX.[2] = 1 )

0

Enable (R/W)

Set 1 to enable L3 CAT masks and COS to

operate in Code and Data Prioritization

(CDP) mode

63:1

Reserved.

C8DH

3213

IA32_QM_EVTSEL

Monitoring Event Select Register (R/W)

If ( CPUID.(EAX=07H,

ECX=0):EBX.[12] = 1 )

7:0

Event ID: ID of a supported monitoring

event to report via IA32_QM_CTR.

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal