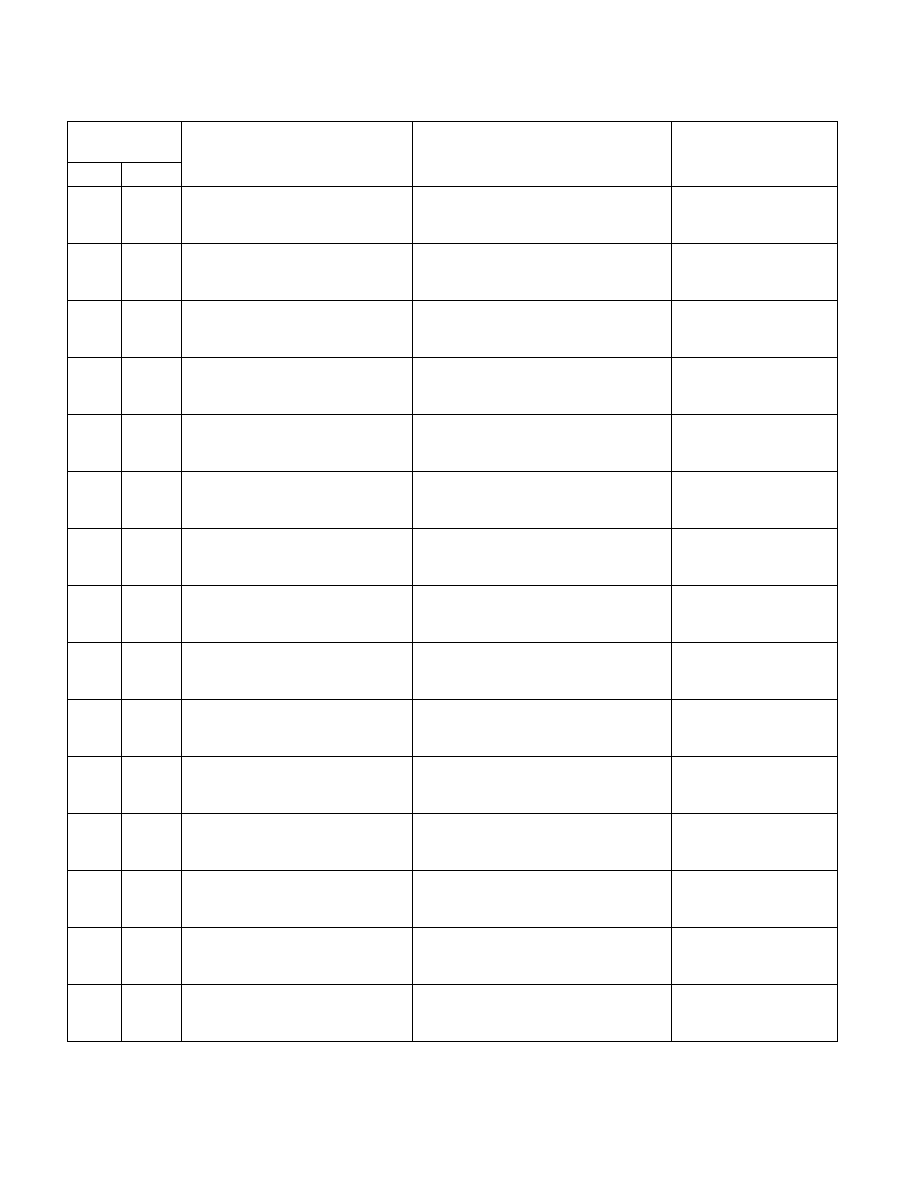

35-38 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

81FH

2079

IA32_X2APIC_TMR7

x2APIC Trigger Mode Register Bits

255:224 (R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

820H

2080

IA32_X2APIC_IRR0

x2APIC Interrupt Request Register Bits

31:0 (R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

821H

2081

IA32_X2APIC_IRR1

x2APIC Interrupt Request Register Bits

63:32 (R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

822H

2082

IA32_X2APIC_IRR2

x2APIC Interrupt Request Register Bits

95:64 (R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

823H

2083

IA32_X2APIC_IRR3

x2APIC Interrupt Request Register Bits

127:96 (R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

824H

2084

IA32_X2APIC_IRR4

x2APIC Interrupt Request Register Bits

159:128 (R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

825H

2085

IA32_X2APIC_IRR5

x2APIC Interrupt Request Register Bits

191:160 (R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

826H

2086

IA32_X2APIC_IRR6

x2APIC Interrupt Request Register Bits

223:192 (R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

827H

2087

IA32_X2APIC_IRR7

x2APIC Interrupt Request Register Bits

255:224 (R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

828H

2088

IA32_X2APIC_ESR

x2APIC Error Status Register (R/W)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

82FH

2095

IA32_X2APIC_LVT_CMCI

x2APIC LVT Corrected Machine Check

Interrupt Register (R/W)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

830H

2096

IA32_X2APIC_ICR

x2APIC Interrupt Command Register

(R/W)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

832H

2098

IA32_X2APIC_LVT_TIMER

x2APIC LVT Timer Interrupt Register

(R/W)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

833H

2099

IA32_X2APIC_LVT_THERMAL

x2APIC LVT Thermal Sensor Interrupt

Register (R/W)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

834H

2100

IA32_X2APIC_LVT_PMI

x2APIC LVT Performance Monitor

Interrupt Register (R/W)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal