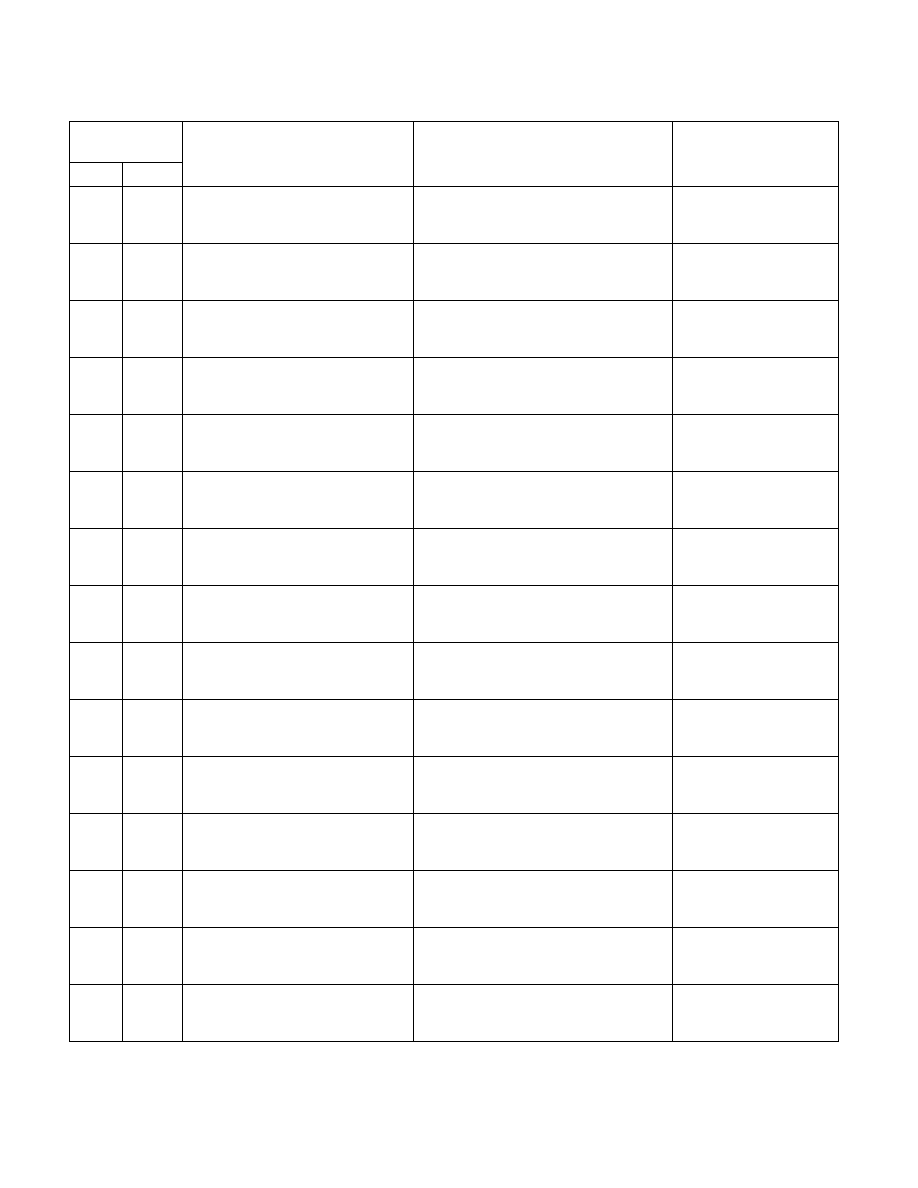

Vol. 3C 35-37

MODEL-SPECIFIC REGISTERS (MSRS)

810H

2064

IA32_X2APIC_ISR0

x2APIC In-Service Register Bits 31:0

(R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

811H

2065

IA32_X2APIC_ISR1

x2APIC In-Service Register Bits 63:32

(R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

812H

2066

IA32_X2APIC_ISR2

x2APIC In-Service Register Bits 95:64

(R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

813H

2067

IA32_X2APIC_ISR3

x2APIC In-Service Register Bits 127:96

(R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

814H

2068

IA32_X2APIC_ISR4

x2APIC In-Service Register Bits 159:128

(R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

815H

2069

IA32_X2APIC_ISR5

x2APIC In-Service Register Bits 191:160

(R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

816H

2070

IA32_X2APIC_ISR6

x2APIC In-Service Register Bits 223:192

(R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

817H

2071

IA32_X2APIC_ISR7

x2APIC In-Service Register Bits 255:224

(R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

818H

2072

IA32_X2APIC_TMR0

x2APIC Trigger Mode Register Bits 31:0

(R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

819H

2073

IA32_X2APIC_TMR1

x2APIC Trigger Mode Register Bits 63:32

(R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

81AH

2074

IA32_X2APIC_TMR2

x2APIC Trigger Mode Register Bits 95:64

(R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

81BH

2075

IA32_X2APIC_TMR3

x2APIC Trigger Mode Register Bits

127:96 (R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

81CH

2076

IA32_X2APIC_TMR4

x2APIC Trigger Mode Register Bits

159:128 (R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

81DH

2077

IA32_X2APIC_TMR5

x2APIC Trigger Mode Register Bits

191:160 (R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

81EH

2078

IA32_X2APIC_TMR6

x2APIC Trigger Mode Register Bits

223:192 (R/O)

If ( CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1)

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal