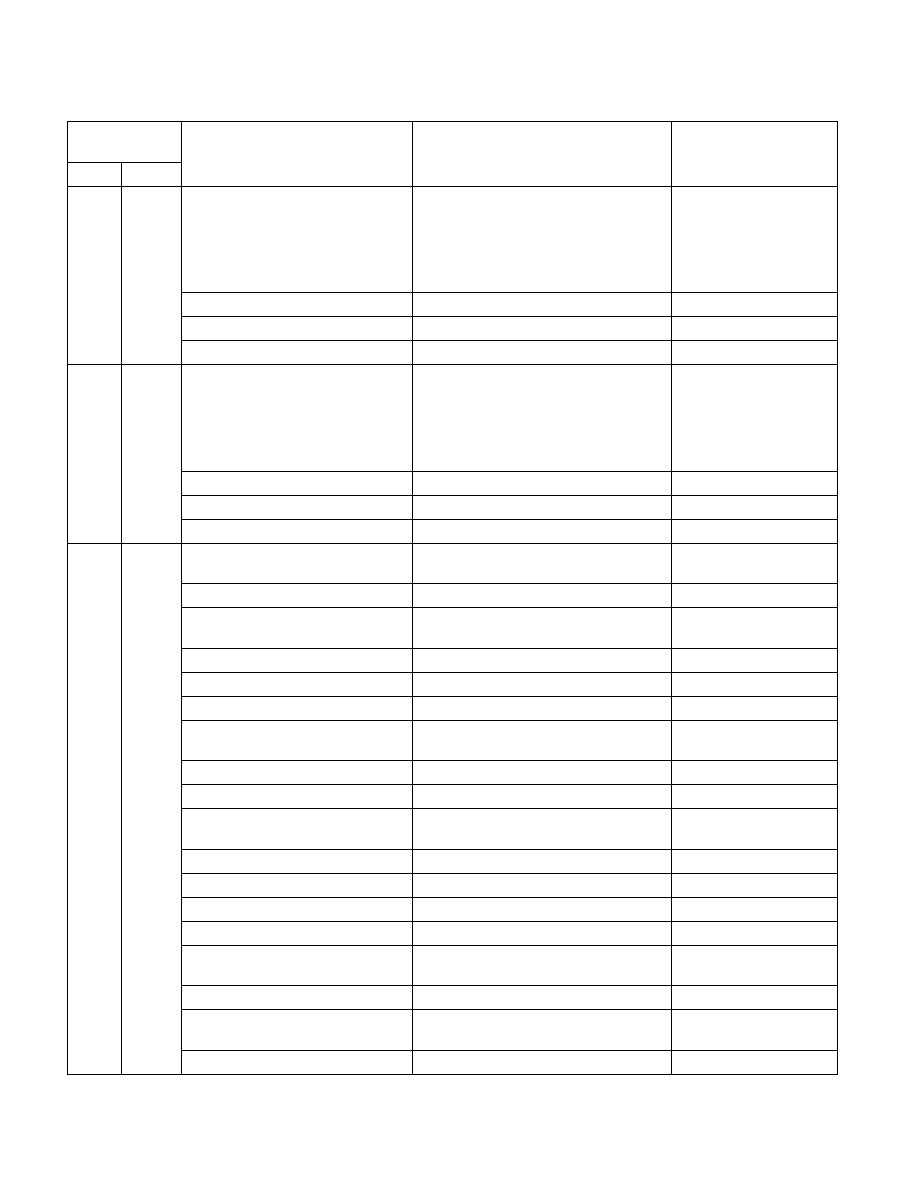

35-32 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

560H

1376

IA32_RTIT_OUTPUT_BASE

Trace Output Base Register (R/W)

If ((CPUID.(EAX=07H,

ECX=0):EBX[25] = 1) && (

(CPUID.(EAX=14H,ECX=0):

ECX[0] = 1) ||

(CPUID.(EAX=14H,ECX=0):

ECX[2] = 1) ) )

6:0

Reserved

MAXPHYADDR

3

-1:7

Base physical address

63:MAXPHYADDR

Reserved.

561H

1377

IA32_RTIT_OUTPUT_MASK_PTRS

Trace Output Mask Pointers Register

(R/W)

If ((CPUID.(EAX=07H,

ECX=0):EBX[25] = 1) && (

(CPUID.(EAX=14H,ECX=0):

ECX[0] = 1) ||

(CPUID.(EAX=14H,ECX=0):

ECX[2] = 1) ) )

6:0

Reserved

31:7

MaskOrTableOffset

63:32

Output Offset.

570H

1392

IA32_RTIT_CTL

Trace Control Register (R/W)

If (CPUID.(EAX=07H,

ECX=0):EBX[25] = 1)

0

TraceEn

1

CYCEn

If (CPUID.(EAX=07H,

ECX=0):EBX[1] = 1)

2

OS

3

User

5:4

Reserved,

6

FabricEn

If (CPUID.(EAX=07H,

ECX=0):ECX[3] = 1)

7

CR3 filter

8

ToPA

9

MTCEn

If (CPUID.(EAX=07H,

ECX=0):EBX[3] = 1)

10

TSCEn

11

DisRETC

12

Reserved, MBZ

13

BranchEn

17:14

MTCFreq

If (CPUID.(EAX=07H,

ECX=0):EBX[3] = 1)

18

Reserved, MBZ

22:19

CYCThresh

If (CPUID.(EAX=07H,

ECX=0):EBX[1] = 1)

23

Reserved, MBZ

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal