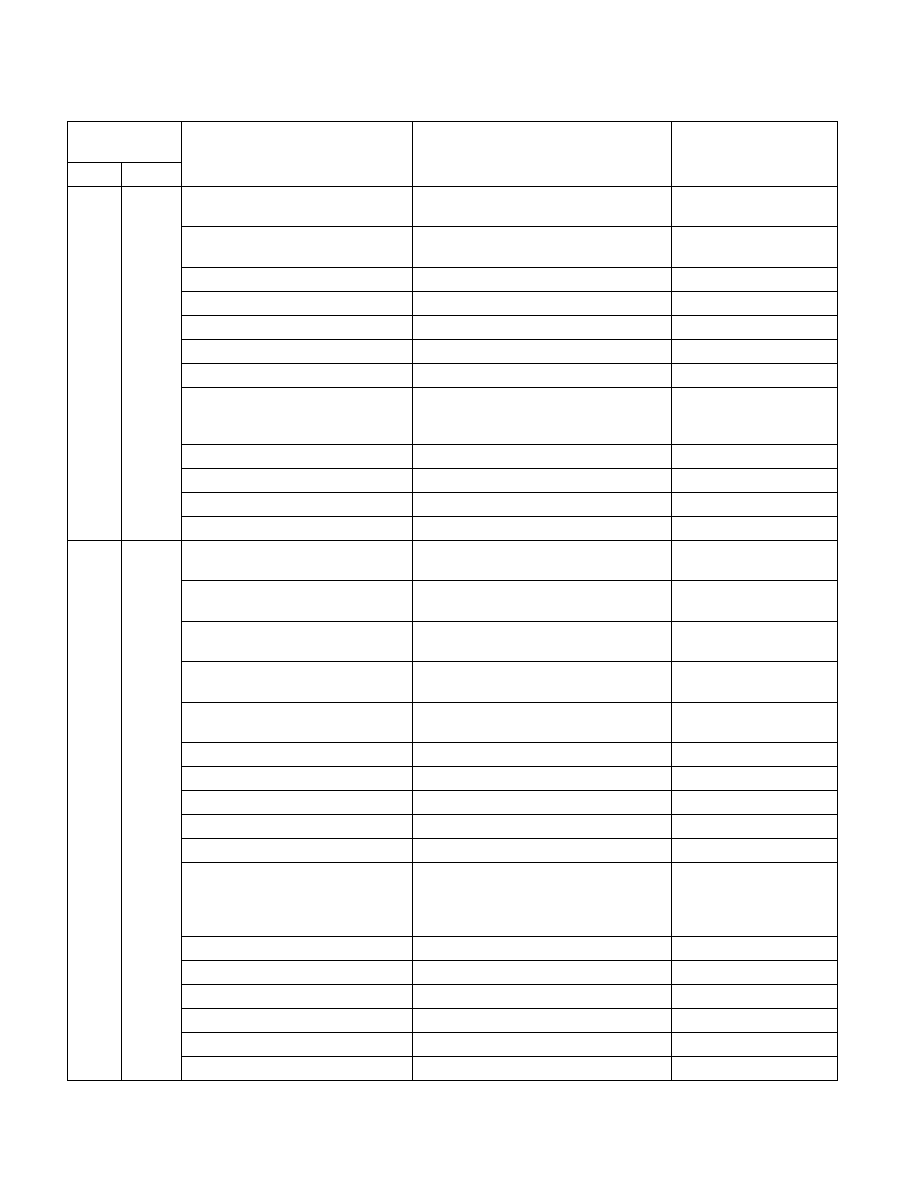

35-24 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

2

Set 1 to Clear Ovf_PMC2 bit.

If CPUID.0AH: EAX[15:8] >

2

n

Set 1 to Clear Ovf_PMCn bit.

If CPUID.0AH: EAX[15:8] >

n

31:n

Reserved.

32

Set 1 to Clear Ovf_FIXED_CTR0 bit.

If CPUID.0AH: EDX[4:0] > 0

33

Set 1 to Clear Ovf_FIXED_CTR1 bit.

If CPUID.0AH: EDX[4:0] > 1

34

Set 1 to Clear Ovf_FIXED_CTR2 bit.

If CPUID.0AH: EDX[4:0] > 2

54:35

Reserved.

55

Set 1 to Clear Trace_ToPA_PMI bit.

If (CPUID.(EAX=07H,

ECX=0):EBX[25] = 1) &&

IA32_RTIT_CTL.ToPA = 1

60:56

Reserved.

61

Set 1 to Clear Ovf_Uncore bit.

06_2EH

62

Set 1 to Clear OvfBuf: bit.

If CPUID.0AH: EAX[7:0] > 0

63

Set to 1to clear CondChgd: bit.

If CPUID.0AH: EAX[7:0] > 0

390H

912

IA32_PERF_GLOBAL_STATUS_RESET

Global Performance Counter Overflow

Reset Control (R/W)

If CPUID.0AH: EAX[7:0] > 3

0

Set 1 to Clear Ovf_PMC0 bit.

If CPUID.0AH: EAX[15:8] >

0

1

Set 1 to Clear Ovf_PMC1 bit.

If CPUID.0AH: EAX[15:8] >

1

2

Set 1 to Clear Ovf_PMC2 bit.

If CPUID.0AH: EAX[15:8] >

2

n

Set 1 to Clear Ovf_PMCn bit.

If CPUID.0AH: EAX[15:8] >

n

31:n

Reserved.

32

Set 1 to Clear Ovf_FIXED_CTR0 bit.

If CPUID.0AH: EDX[4:0] > 0

33

Set 1 to Clear Ovf_FIXED_CTR1 bit.

If CPUID.0AH: EDX[4:0] > 1

34

Set 1 to Clear Ovf_FIXED_CTR2 bit.

If CPUID.0AH: EDX[4:0] > 2

54:35

Reserved.

55

Set 1 to Clear Trace_ToPA_PMI bit.

If (CPUID.(EAX=07H,

ECX=0):EBX[25] = 1) &&

IA32_RTIT_CTL.ToPA[8] =

1

57:56

Reserved.

58

Set 1 to Clear LBR_Frz bit.

If CPUID.0AH: EAX[7:0] > 3

59

Set 1 to Clear CTR_Frz bit.

If CPUID.0AH: EAX[7:0] > 3

58

Set 1 to Clear ASCI bit.

If CPUID.0AH: EAX[7:0] > 3

61

Set 1 to Clear Ovf_Uncore bit.

06_2EH

62

Set 1 to Clear OvfBuf: bit.

If CPUID.0AH: EAX[7:0] > 0

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal