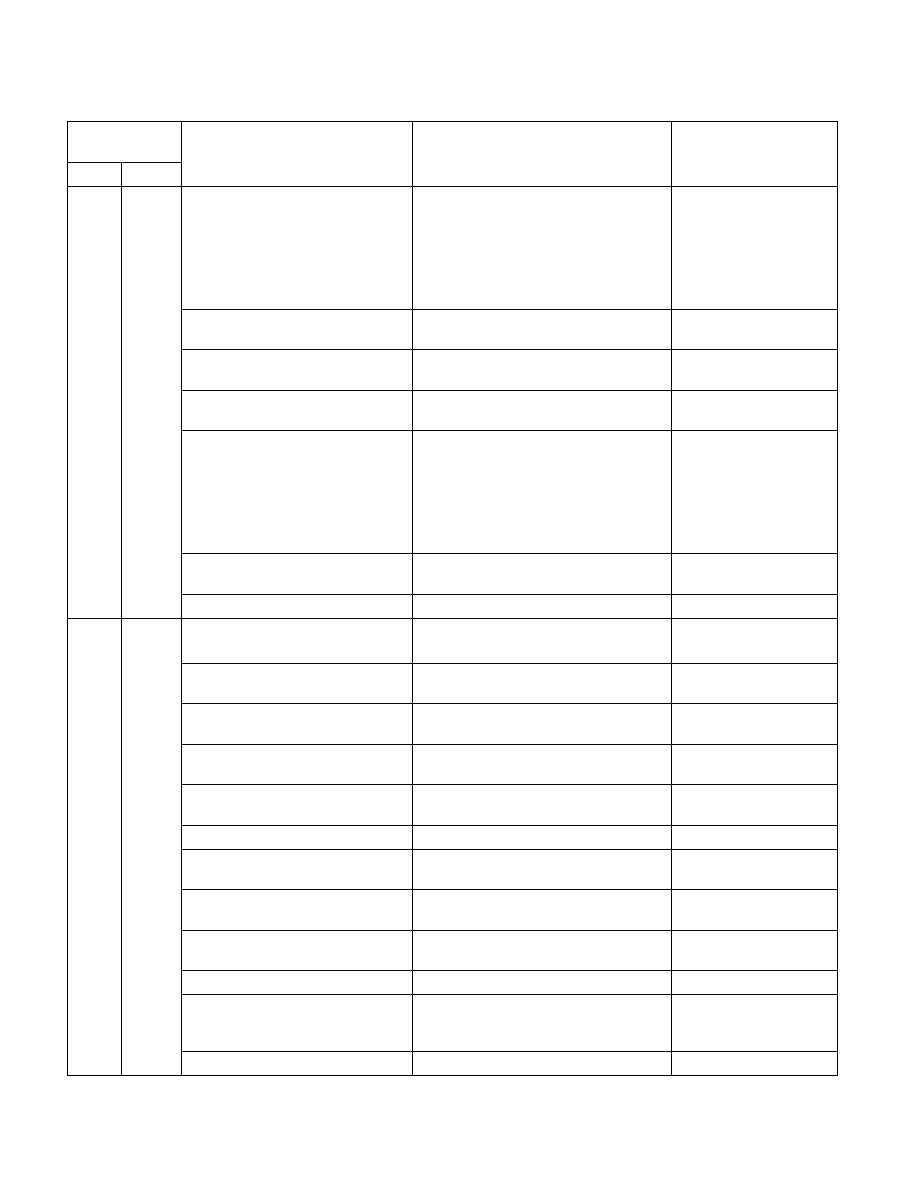

35-22 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

6

AnyThread: When set to 1, it enables

counting the associated event conditions

occurring across all logical processors

sharing a processor core. When set to 0, the

counter only increments the associated

event conditions occurring in the logical

processor which programmed the MSR.

If CPUID.0AH:

EAX[7:0] > 2

7

EN1_PMI: Enable PMI when fixed counter 1

overflows.

8

EN2_OS: Enable Fixed Counter 2 to count

while CPL = 0.

9

EN2_Usr: Enable Fixed Counter 2 to count

while CPL > 0.

10

AnyThread: When set to 1, it enables

counting the associated event conditions

occurring across all logical processors

sharing a processor core. When set to 0, the

counter only increments the associated

event conditions occurring in the logical

processor which programmed the MSR.

If CPUID.0AH:

EAX[7:0] > 2

11

EN2_PMI: Enable PMI when fixed counter 2

overflows.

63:12

Reserved.

38EH

910

IA32_PERF_GLOBAL_STATUS

Global Performance Counter Status (RO)

If CPUID.0AH: EAX[7:0] > 0

0

Ovf_PMC0: Overflow status of IA32_PMC0. If CPUID.0AH: EAX[15:8] >

0

1

Ovf_PMC1: Overflow status of IA32_PMC1. If CPUID.0AH: EAX[15:8] >

1

2

Ovf_PMC2: Overflow status of IA32_PMC2. If CPUID.0AH: EAX[15:8] >

2

3

Ovf_PMC3: Overflow status of IA32_PMC3. If CPUID.0AH: EAX[15:8] >

3

31:4

Reserved.

32

Ovf_FixedCtr0: Overflow status of

IA32_FIXED_CTR0.

If CPUID.0AH: EAX[7:0] > 1

33

Ovf_FixedCtr1: Overflow status of

IA32_FIXED_CTR1.

If CPUID.0AH: EAX[7:0] > 1

34

Ovf_FixedCtr2: Overflow status of

IA32_FIXED_CTR2.

If CPUID.0AH: EAX[7:0] > 1

54:35

Reserved.

55

Trace_ToPA_PMI: A PMI occurred due to a

ToPA entry memory buffer was completely

filled.

If (CPUID.(EAX=07H,

ECX=0):EBX[25] = 1) &&

IA32_RTIT_CTL.ToPA = 1

57:56

Reserved.

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal