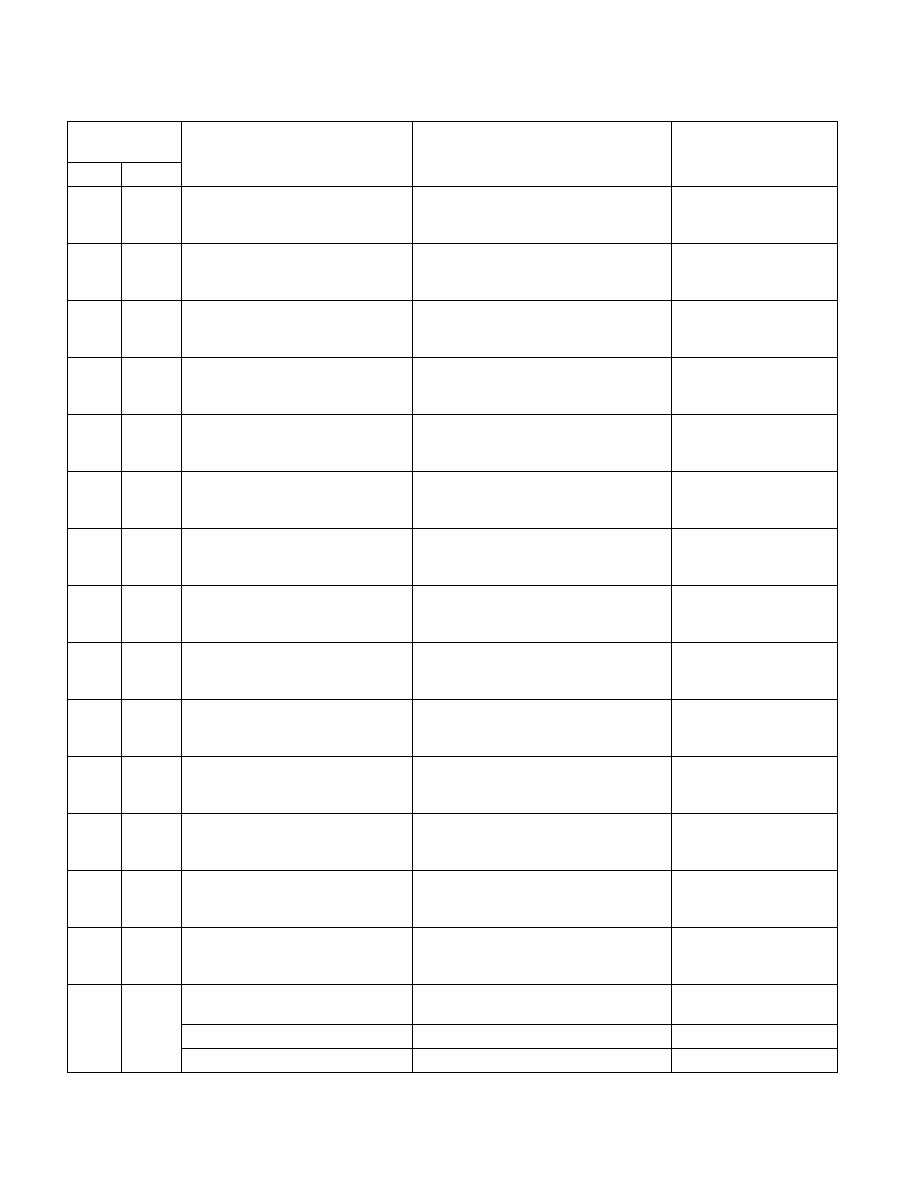

35-20 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

292H

658

IA32_MC18_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

18

293H

659

IA32_MC19_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

19

294H

660

IA32_MC20_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

20

295H

661

IA32_MC21_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

21

296H

662

IA32_MC22_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

22

297H

663

IA32_MC23_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

23

298H

664

IA32_MC24_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

24

299H

665

IA32_MC25_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

25

29AH

666

IA32_MC26_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

26

29BH

667

IA32_MC27_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

27

29CH

668

IA32_MC28_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

28

29DH

669

IA32_MC29_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

29

29EH

670

IA32_MC30_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

30

29FH

671

IA32_MC31_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

31

2FFH

767

IA32_MTRR_DEF_TYPE

MTRRdefType (R/W)

If CPUID.01H:

EDX.MTRR[12] =1

2:0

Default Memory Type

9:3

Reserved.

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal