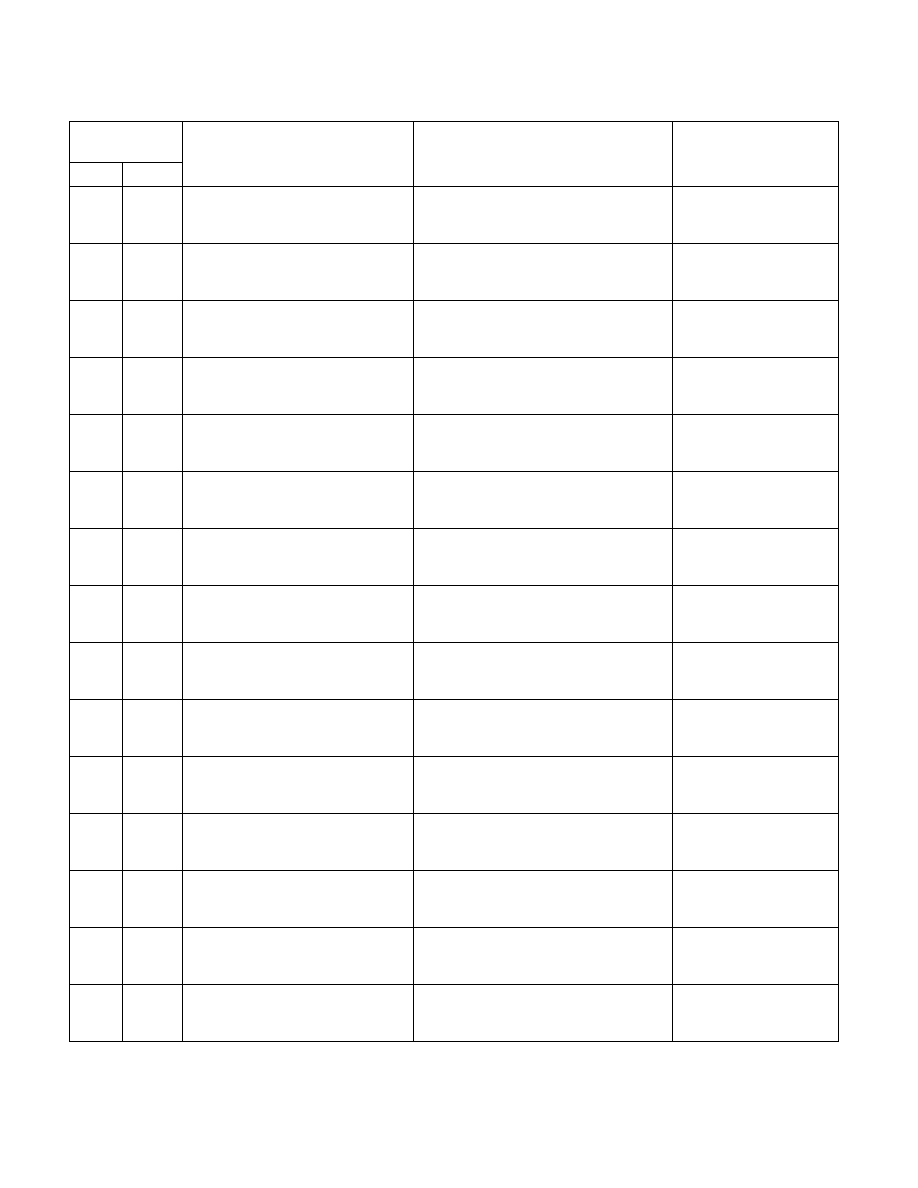

Vol. 3C 35-19

MODEL-SPECIFIC REGISTERS (MSRS)

283H

643

IA32_MC3_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

3

284H

644

IA32_MC4_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

4

285H

645

IA32_MC5_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

5

286H

646

IA32_MC6_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

6

287H

647

IA32_MC7_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

7

288H

648

IA32_MC8_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

8

289H

649

IA32_MC9_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

9

28AH

650

IA32_MC10_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

10

28BH

651

IA32_MC11_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

11

28CH

652

IA32_MC12_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

12

28DH

653

IA32_MC13_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

13

28EH

654

IA32_MC14_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

14

28FH

655

IA32_MC15_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

15

290H

656

IA32_MC16_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

16

291H

657

IA32_MC17_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

17

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal