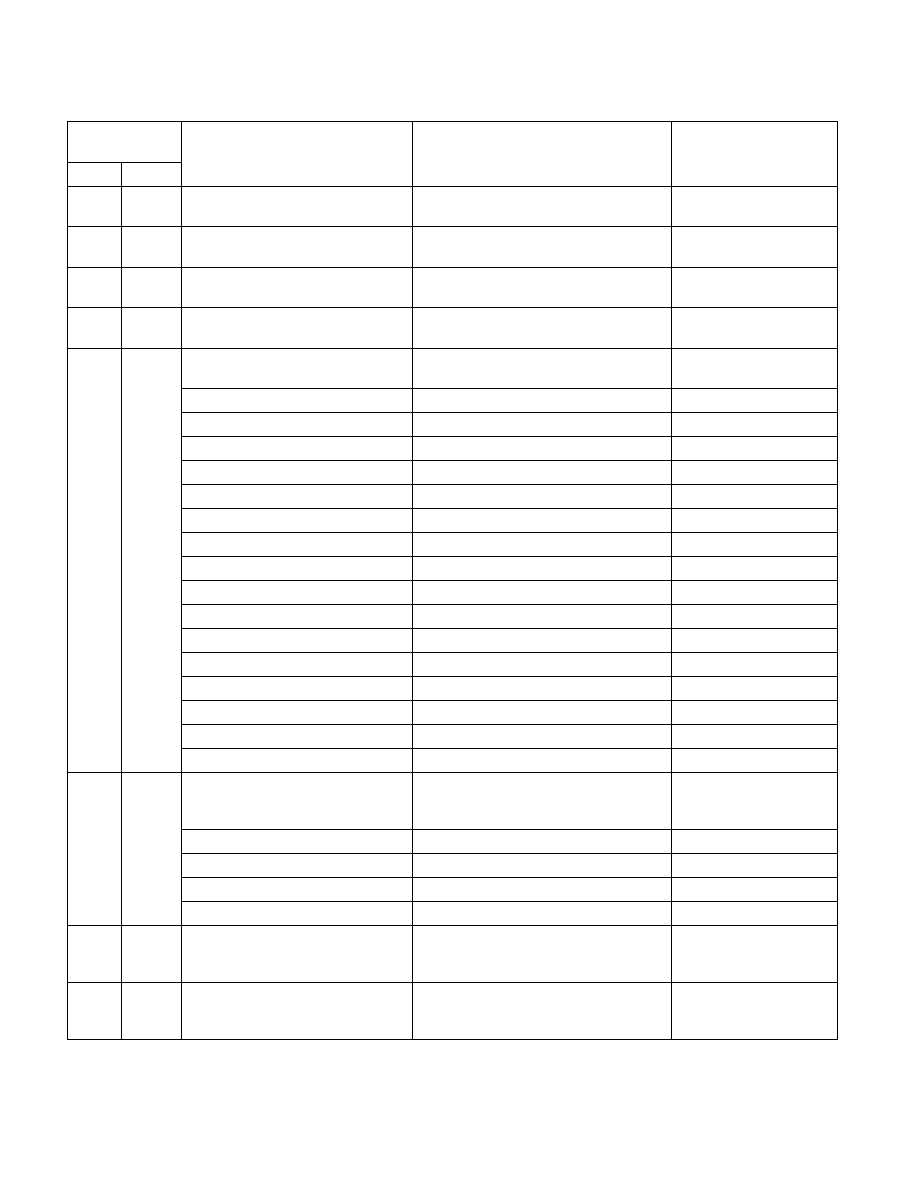

35-18 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

26CH

620

IA32_MTRR_FIX4K_E0000

MTRRfix4K_E0000

If CPUID.01H:

EDX.MTRR[12] =1

26DH

621

IA32_MTRR_FIX4K_E8000

MTRRfix4K_E8000

If CPUID.01H:

EDX.MTRR[12] =1

26EH

622

IA32_MTRR_FIX4K_F0000

MTRRfix4K_F0000

If CPUID.01H:

EDX.MTRR[12] =1

26FH

623

IA32_MTRR_FIX4K_F8000

MTRRfix4K_F8000

If CPUID.01H:

EDX.MTRR[12] =1

277H

631

IA32_PAT

IA32_PAT (R/W)

If CPUID.01H:

EDX.MTRR[16] =1

2:0

PA0

7:3

Reserved.

10:8

PA1

15:11

Reserved.

18:16

PA2

23:19

Reserved.

26:24

PA3

31:27

Reserved.

34:32

PA4

39:35

Reserved.

42:40

PA5

47:43

Reserved.

50:48

PA6

55:51

Reserved.

58:56

PA7

63:59

Reserved.

280H

640

IA32_MC0_CTL2

(R/W)

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

0

14:0

Corrected error count threshold.

29:15

Reserved.

30

CMCI_EN

63:31

Reserved.

281H

641

IA32_MC1_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

1

282H

642

IA32_MC2_CTL2

(R/W) same fields as IA32_MC0_CTL2.

If IA32_MCG_CAP[10] = 1

&& IA32_MCG_CAP[7:0] >

2

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal