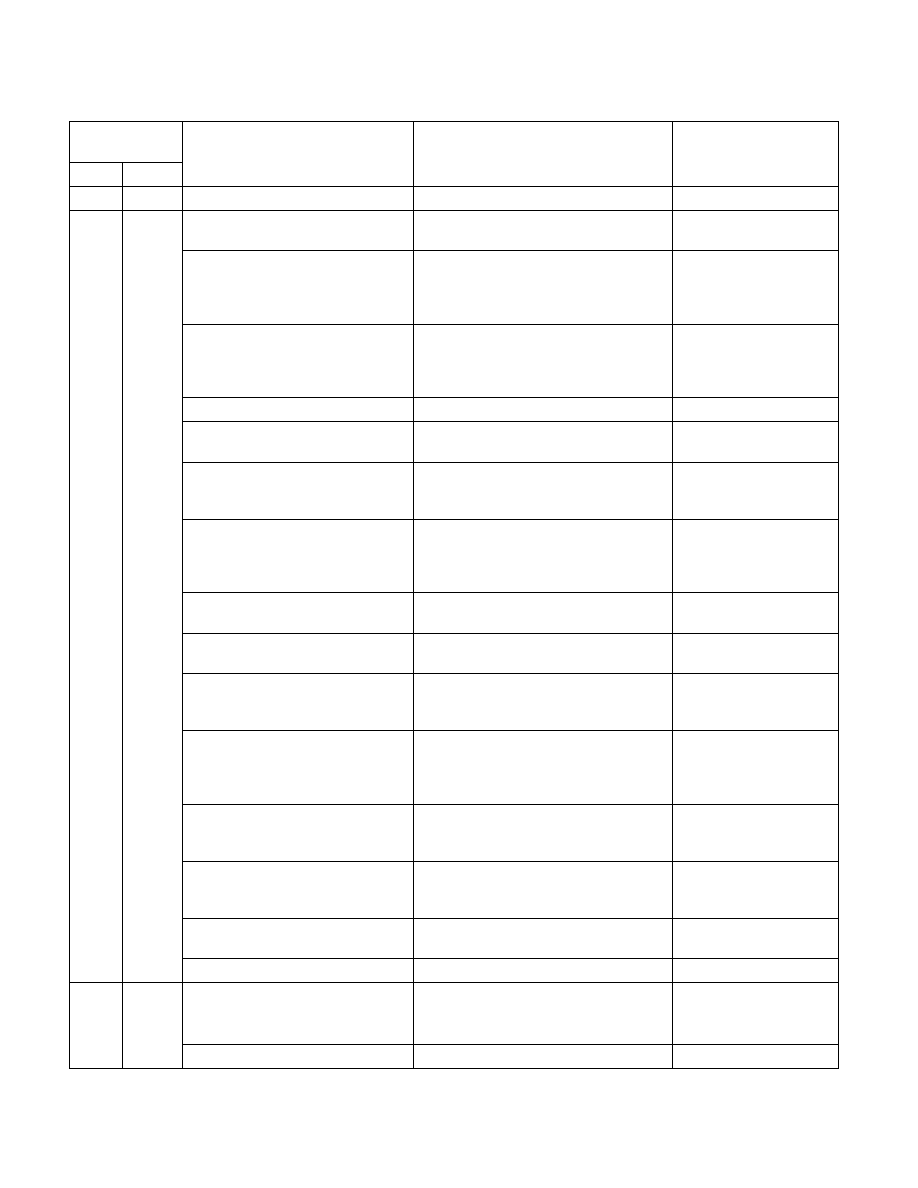

Vol. 3C 35-15

MODEL-SPECIFIC REGISTERS (MSRS)

63:25

Reserved.

1D9H

473

IA32_DEBUGCTL (MSR_DEBUGCTLA,

MSR_DEBUGCTLB)

Trace/Profile Resource Control (R/W)

06_0EH

0

LBR: Setting this bit to 1 enables the

processor to record a running trace of the

most recent branches taken by the

processor in the LBR stack.

06_01H

1

BTF: Setting this bit to 1 enables the

processor to treat EFLAGS.TF as single-step

on branches instead of single-step on

instructions.

06_01H

5:2

Reserved.

6

TR: Setting this bit to 1 enables branch

trace messages to be sent.

06_0EH

7

BTS: Setting this bit enables branch trace

messages (BTMs) to be logged in a BTS

buffer.

06_0EH

8

BTINT: When clear, BTMs are logged in a

BTS buffer in circular fashion. When this bit

is set, an interrupt is generated by the BTS

facility when the BTS buffer is full.

06_0EH

9

1: BTS_OFF_OS: When set, BTS or BTM is

skipped if CPL = 0.

06_0FH

10

BTS_OFF_USR: When set, BTS or BTM is

skipped if CPL > 0.

06_0FH

11

FREEZE_LBRS_ON_PMI: When set, the LBR

stack is frozen on a PMI request.

If CPUID.01H: ECX[15] = 1

&& CPUID.0AH: EAX[7:0] >

1

12

FREEZE_PERFMON_ON_PMI: When set,

each ENABLE bit of the global counter

control MSR are frozen (address 38FH) on a

PMI request

If CPUID.01H: ECX[15] = 1

&& CPUID.0AH: EAX[7:0] >

1

13

ENABLE_UNCORE_PMI: When set, enables

the logical processor to receive and

generate PMI on behalf of the uncore.

06_1AH

14

FREEZE_WHILE_SMM: When set, freezes

perfmon and trace messages while in SMM.

If

IA32_PERF_CAPABILITIES[

12] = 1

15

RTM_DEBUG: When set, enables DR7 debug

bit on XBEGIN

If (CPUID.(EAX=07H,

ECX=0):EBX[11] = 1)

63:16

Reserved.

1F2H

498

IA32_SMRR_PHYSBASE

SMRR Base Address (Writeable only in

SMM)

Base address of SMM memory range.

If

IA32_MTRRCAP.SMRR[11]

= 1

7:0

Type. Specifies memory type of the range.

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal