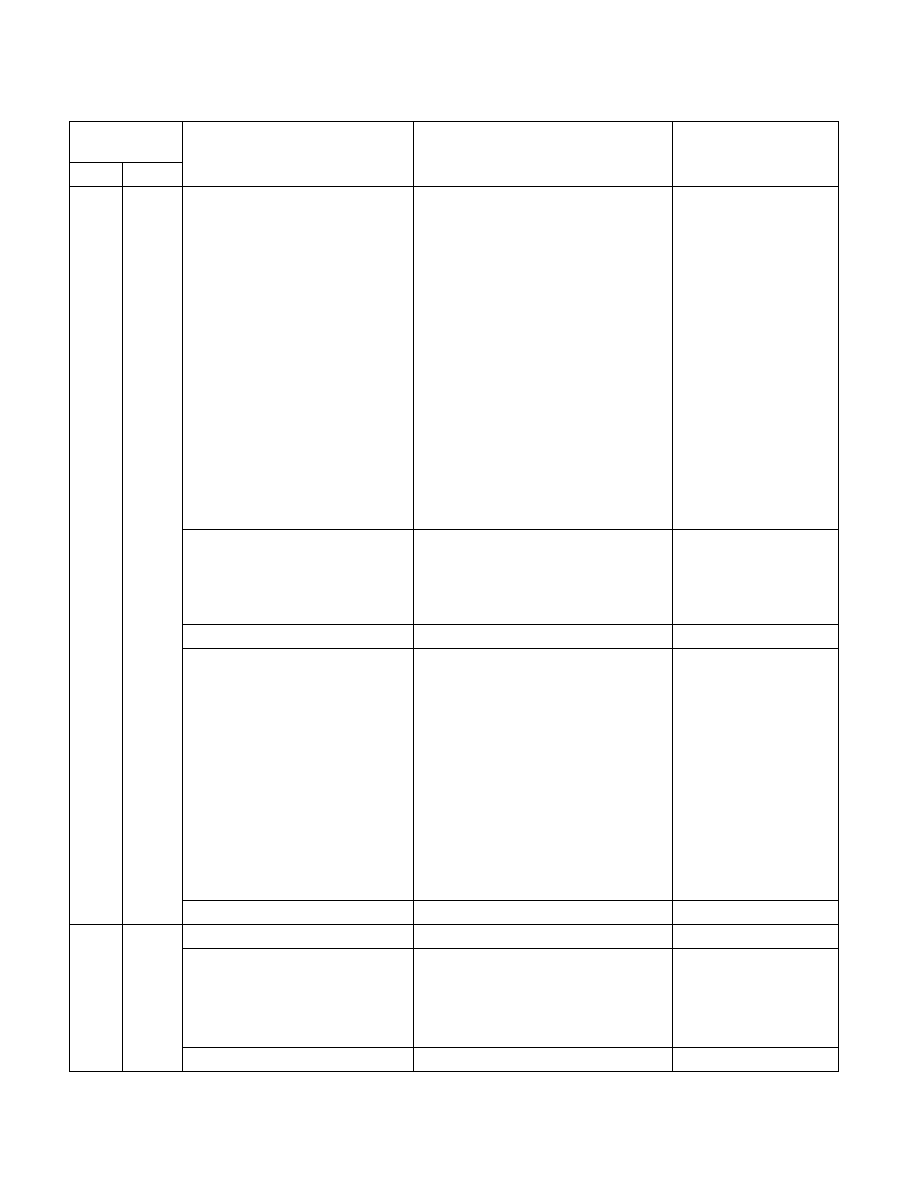

Vol. 3C 35-13

MODEL-SPECIFIC REGISTERS (MSRS)

22

Limit CPUID Maxval (R/W)

When this bit is set to 1, CPUID.00H returns

a maximum value in EAX[7:0] of 2.

BIOS should contain a setup question that

allows users to specify when the installed

OS does not support CPUID functions

greater than 2.

Before setting this bit, BIOS must execute

the CPUID.0H and examine the maximum

value returned in EAX[7:0]. If the maximum

value is greater than 2, this bit is

supported.

Otherwise, this bit is not supported. Setting

this bit when the maximum value is not

greater than 2 may generate a #GP

exception.

Setting this bit may cause unexpected

behavior in software that depends on the

availability of CPUID leaves greater than 2.

0F_03H

23

xTPR Message Disable (R/W)

When set to 1, xTPR messages are

disabled. xTPR messages are optional

messages that allow the processor to

inform the chipset of its priority.

if CPUID.01H:ECX[14] = 1

33:24

Reserved.

34

XD Bit Disable (R/W)

When set to 1, the Execute Disable Bit

feature (XD Bit) is disabled and the XD Bit

extended feature flag will be clear

(CPUID.80000001H: EDX[20]=0).

When set to a 0 (default), the Execute

Disable Bit feature (if available) allows the

OS to enable PAE paging and take

advantage of data only pages.

BIOS must not alter the contents of this bit

location, if XD bit is not supported. Writing

this bit to 1 when the XD Bit extended

feature flag is set to 0 may generate a #GP

exception.

if

CPUID.80000001H:EDX[2

0] = 1

63:35

Reserved.

1B0H

432

IA32_ENERGY_PERF_BIAS

Performance Energy Bias Hint (R/W)

if CPUID.6H:ECX[3] = 1

3:0

Power Policy Preference:

0 indicates preference to highest

performance.

15 indicates preference to maximize

energy saving.

63:4

Reserved.

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal