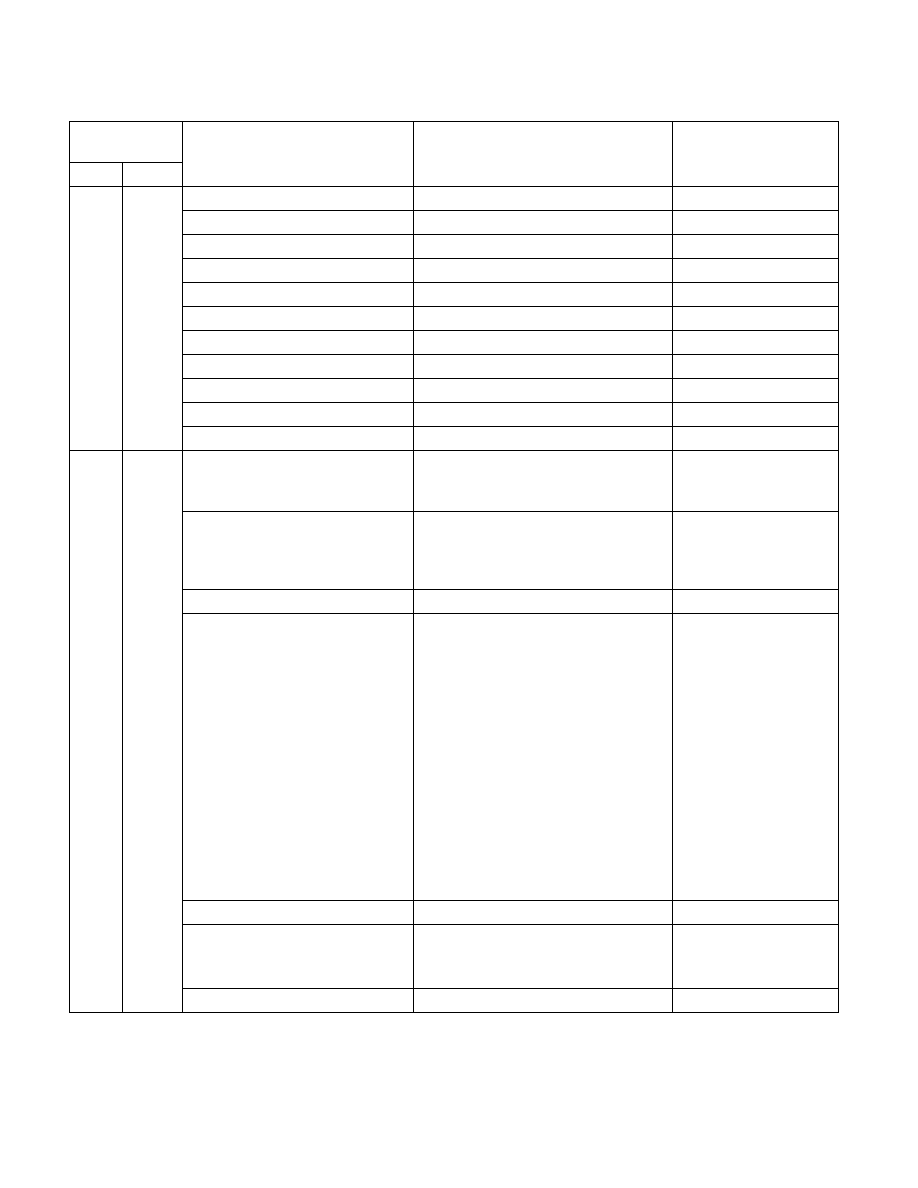

Vol. 3C 35-11

MODEL-SPECIFIC REGISTERS (MSRS)

10

Power Limitation Status (RO)

If CPUID.06H:EAX[4] = 1

11

Power Limitation log (R/WC0)

If CPUID.06H:EAX[4] = 1

12

Current Limit Status (RO)

If CPUID.06H:EAX[7] = 1

13

Current Limit log (R/WC0)

If CPUID.06H:EAX[7] = 1

14

Cross Domain Limit Status (RO)

If CPUID.06H:EAX[7] = 1

15

Cross Domain Limit log (R/WC0)

If CPUID.06H:EAX[7] = 1

22:16

Digital Readout (RO)

If CPUID.06H:EAX[0] = 1

26:23

Reserved.

30:27

Resolution in Degrees Celsius (RO)

If CPUID.06H:EAX[0] = 1

31

Reading Valid (RO)

If CPUID.06H:EAX[0] = 1

63:32

Reserved.

1A0H

416

IA32_MISC_ENABLE

Enable Misc. Processor Features (R/W)

Allows a variety of processor functions to

be enabled and disabled.

0

Fast-Strings Enable

When set, the fast-strings feature (for REP

MOVS and REP STORS) is enabled (default);

when clear, fast-strings are disabled.

0F_0H

2:1

Reserved.

3

Automatic Thermal Control Circuit Enable

(R/W)

1 = Setting this bit enables the thermal

control circuit (TCC) portion of the

Intel Thermal Monitor feature. This

allows the processor to automatically

reduce power consumption in

response to TCC activation.

0 = Disabled.

Note: In some products clearing this bit

might be ignored in critical thermal

conditions, and TM1, TM2 and adaptive

thermal throttling will still be activated.

The default value of this field varies with

product . See respective tables where

default value is listed.

0F_0H

6:4

Reserved

7

Performance Monitoring Available (R)

1 = Performance monitoring enabled

0 = Performance monitoring disabled

0F_0H

10:8

Reserved.

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal