35-8 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

11

MCG_TES_P: Threshold-based error status

register are present if this bit is set.

15:12

Reserved

23:16

MCG_EXT_CNT: Number of extended

machine check state registers present.

24

MCG_SER_P: The processor supports

software error recovery if this bit is set.

25

Reserved.

26

MCG_ELOG_P: Indicates that the processor

allows platform firmware to be invoked

when an error is detected so that it may

provide additional platform specific

information in an ACPI format “Generic

Error Data Entry” that augments the data

included in machine check bank registers.

06_3EH

27

MCG_LMCE_P: Indicates that the processor

support extended state in

IA32_MCG_STATUS and associated

MSR necessary to configure Local

Machine Check Exception (LMCE)

.

06_3EH

63:28

Reserved.

17AH

378

IA32_MCG_STATUS (MCG_STATUS)

Global Machine Check Status (R/W0)

06_01H

0

RIPV. Restart IP valid

06_01H

1

EIPV. Error IP valid

06_01H

2

MCIP. Machine check in progress

06_01H

3

LMCE_S.

If

IA32_MCG_CAP.LMCE_P[2

7] =1

63:4

Reserved.

17BH

379

IA32_MCG_CTL (MCG_CTL)

Global Machine Check Control (R/W)

If IA32_MCG_CAP.CTL_P[8]

=1

180H-

185H

384-

389

Reserved

06_0EH

1

186H

390

IA32_PERFEVTSEL0 (PERFEVTSEL0)

Performance Event Select Register 0 (R/W) If CPUID.0AH: EAX[15:8] >

0

7:0

Event Select: Selects a performance event

logic unit.

15:8

UMask: Qualifies the microarchitectural

condition to detect on the selected event

logic.

16

USR: Counts while in privilege level is not

ring 0.

17

OS: Counts while in privilege level is ring 0.

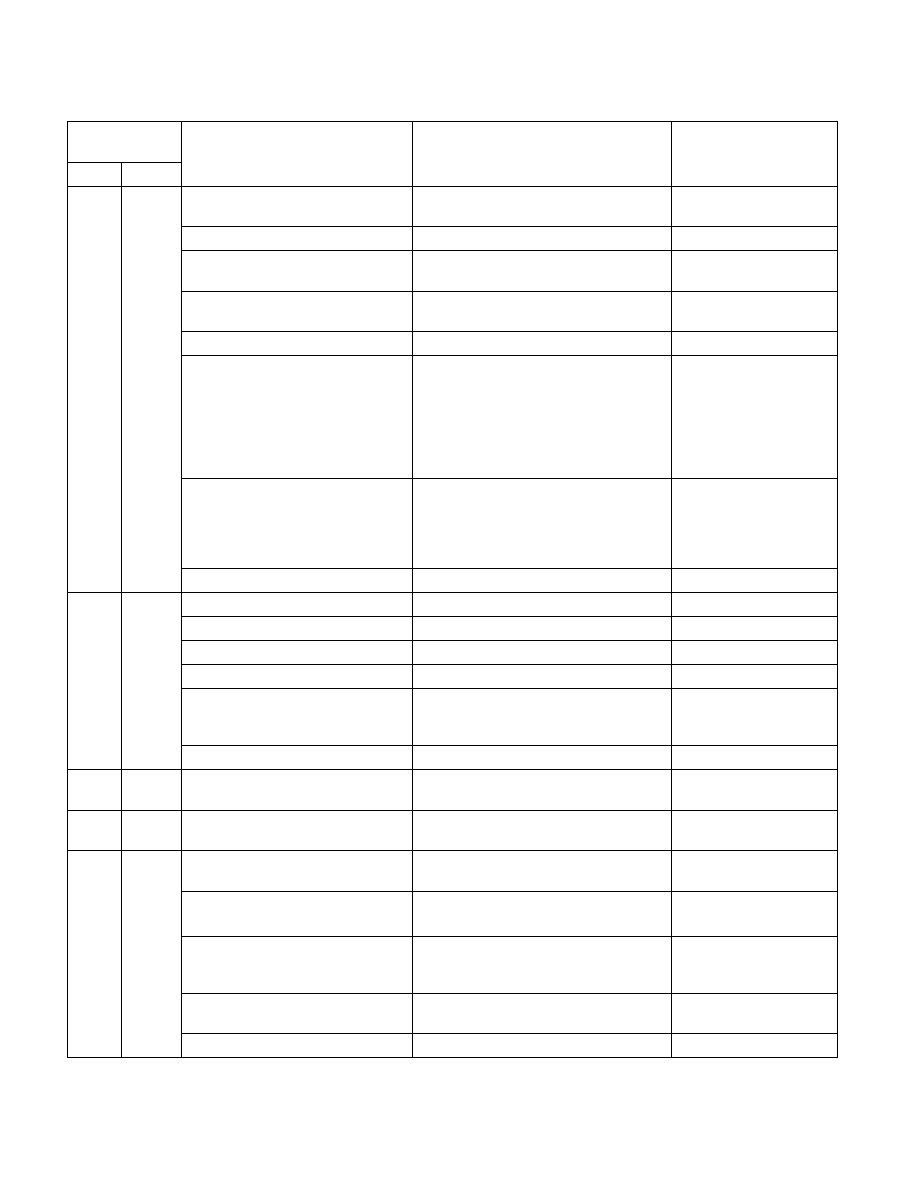

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal