34-8 Vol. 3C

SYSTEM MANAGEMENT MODE

34.4.2 SMRAM

Caching

An IA-32 processor does not automatically write back and invalidate its caches before entering SMM or before

exiting SMM. Because of this behavior, care must be taken in the placement of the SMRAM in system memory and

in the caching of the SMRAM to prevent cache incoherence when switching back and forth between SMM and

protected mode operation. Either of the following three methods of locating the SMRAM in system memory will

guarantee cache coherency:

•

Place the SRAM in a dedicated section of system memory that the operating system and applications are

prevented from accessing. Here, the SRAM can be designated as cacheable (WB, WT, or WC) for optimum

processor performance, without risking cache incoherence when entering or exiting SMM.

•

Place the SRAM in a section of memory that overlaps an area used by the operating system (such as the video

memory), but designate the SMRAM as uncacheable (UC). This method prevents cache access when in SMM to

maintain cache coherency, but the use of uncacheable memory reduces the performance of SMM code.

•

Place the SRAM in a section of system memory that overlaps an area used by the operating system and/or

application code, but explicitly flush (write back and invalidate) the caches upon entering and exiting SMM

mode. This method maintains cache coherency, but incurs the overhead of two complete cache flushes.

For Pentium 4, Intel Xeon, and P6 family processors, a combination of the first two methods of locating the SMRAM

is recommended. Here the SMRAM is split between an overlapping and a dedicated region of memory. Upon

entering SMM, the SMRAM space that is accessed overlaps video memory (typically located in low memory). This

SMRAM section is designated as UC memory. The initial SMM code then jumps to a second SMRAM section that is

located in a dedicated region of system memory (typically in high memory). This SMRAM section can be cached for

optimum processor performance.

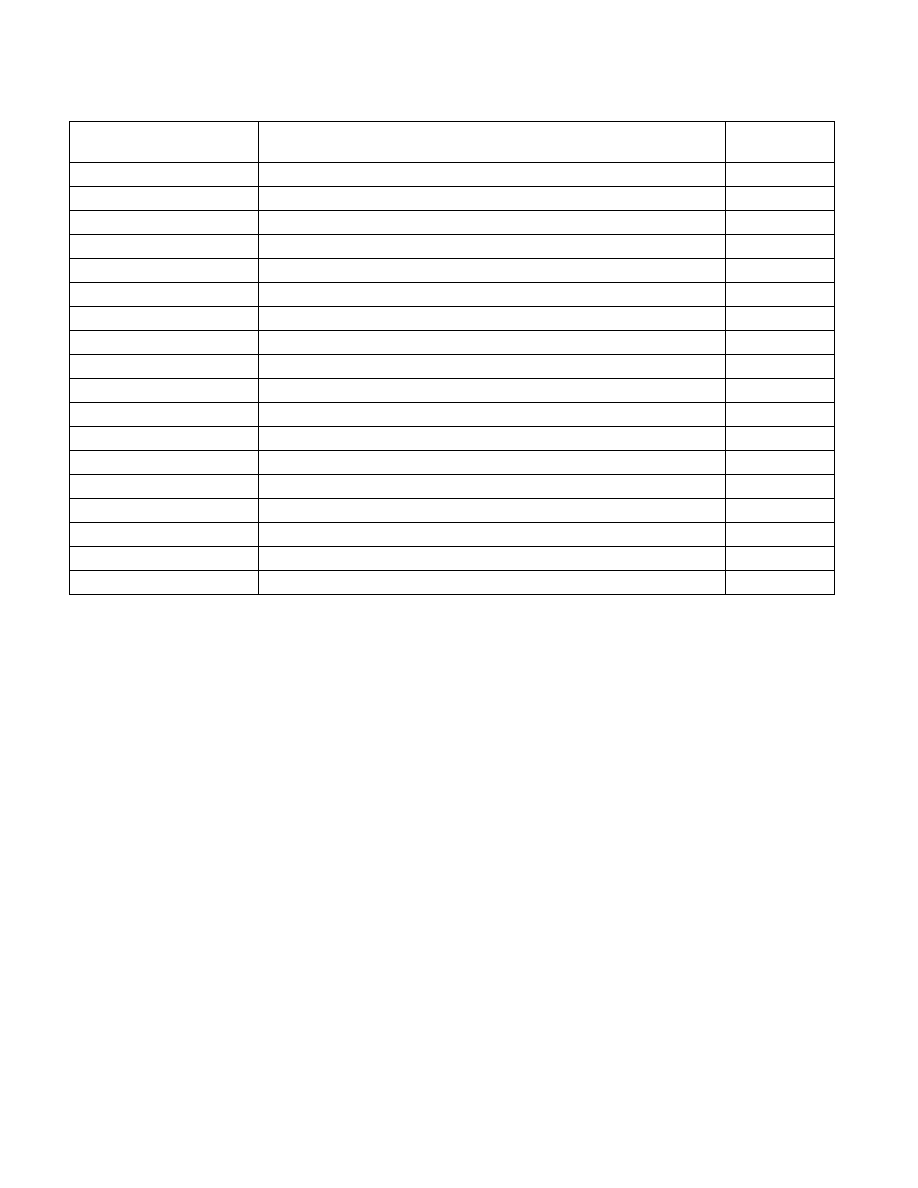

7EF7H - 7EE4H

Reserved

No

7EE0H

Setting of “enable EPT” VM-execution control

No

7ED8H

Value of EPTP VM-execution control field

No

7ED7H - 7EA0H

Reserved

No

7E9CH

LDT Base (lower 32 bits)

No

7E98H

Reserved

No

7E94H

IDT Base (lower 32 bits)

No

7E90H

Reserved

No

7E8CH

GDT Base (lower 32 bits)

No

7E8BH - 7E44H

Reserved

No

7E40H

CR4

No

7E3FH - 7DF0H

Reserved

No

7DE8H

IO_RIP

Yes

7DE7H - 7DDCH

Reserved

No

7DD8H

IDT Base (Upper 32 bits)

No

7DD4H

LDT Base (Upper 32 bits)

No

7DD0H

GDT Base (Upper 32 bits)

No

7DCFH - 7C00H

Reserved

No

NOTE:

1. The two most significant bytes are reserved.

Table 34-3. SMRAM State Save Map for Intel 64 Architecture (Contd.)

Offset

(Added to SMBASE + 8000H)

Register

Writable?