22-26 Vol. 3B

ARCHITECTURE COMPATIBILITY

22.26 INTERRUPTS

The following differences in handling interrupts are found among the IA-32

processors.

22.26.1 Interrupt Propagation Delay

External hardware interrupts may be recognized on different instruction boundaries on the P6 family, Pentium,

Intel486, and Intel386 processors, due to the superscaler designs of the P6 family and Pentium processors. There-

fore, the EIP pushed onto the stack when servicing an interrupt may be different for the P6 family, Pentium,

Intel486, and Intel386 processors.

22.26.2 NMI

Interrupts

After an NMI interrupt is recognized by the P6 family, Pentium, Intel486, Intel386, and Intel 286 processors, the

NMI interrupt is masked until the first IRET instruction is executed, unlike the 8086 processor.

22.26.3 IDT

Limit

The LIDT instruction can be used to set a limit on the size of the IDT. A double-fault exception (#DF) is generated

if an interrupt or exception attempts to read a vector beyond the limit. Shutdown then occurs on the 32-bit IA-32

processors if the double-fault handler vector is beyond the limit. (The 8086 processor does not have a shutdown

mode nor a limit.)

22.27 ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

The Advanced Programmable Interrupt Controller (APIC), referred to in this book as the local APIC, was intro-

duced into the IA-32 processors with the Pentium processor (beginning with the 735/90 and 815/100 models) and

is included in the Pentium 4, Intel Xeon, and P6 family processors. The features and functions of the local APIC are

derived from the Intel 82489DX external APIC, which was used with the Intel486 and early Pentium processors.

Additional refinements of the local APIC architecture were incorporated in the Pentium 4 and Intel Xeon processors.

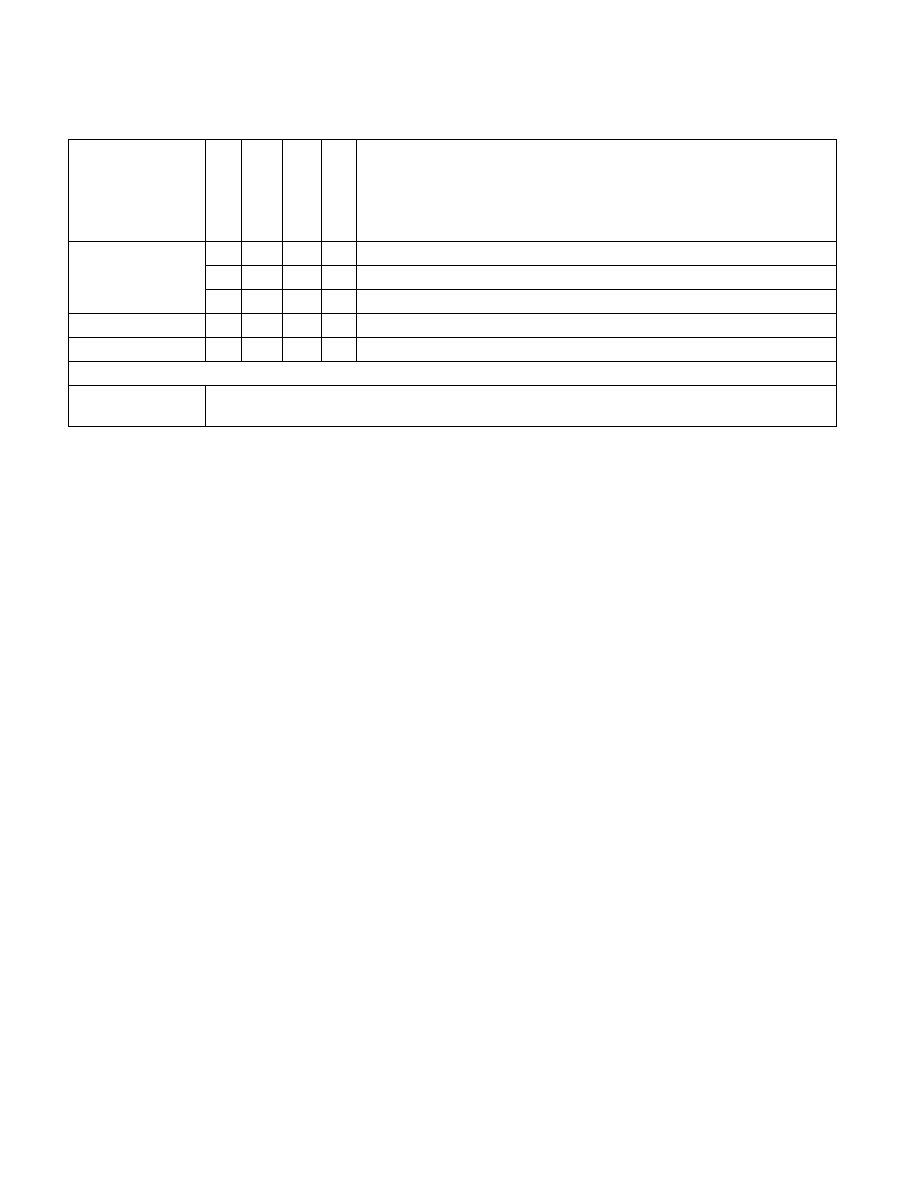

Table 22-9. Exception Conditions for Legacy SIMD/MMX Instructions without Memory Reference

Exception

Re

al

Virtual-8

086

Pr

ot

ected and

Compatibi

lity

64

-bit

Cause of Exception

Invalid Opcode, #UD

X

X

X

X

If CR0.EM[bit 2] = 1.

X

X

X

X

If preceded by a LOCK prefix (F0H)

X

X

X

X

If any corresponding CPUID feature flag is ‘0’

#MF

X

X

X

X

If there is a pending X87 FPU exception

#NM

X

X

If CR0.TS[bit 3]=1

Applicable Instruc-

tions

PEXTRW, PMOVMSKB