Vol. 3B 22-25

ARCHITECTURE COMPATIBILITY

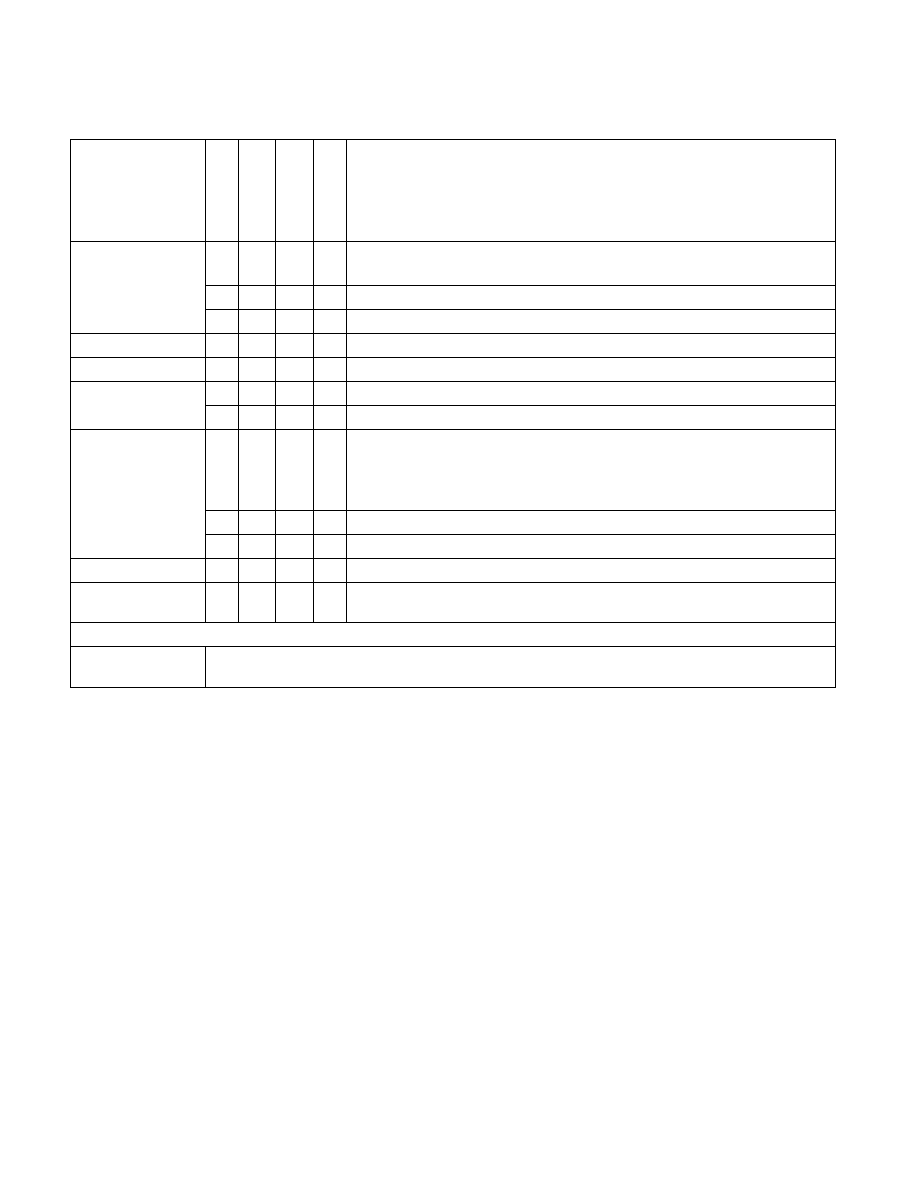

Table 22-8. Exception Conditions for Legacy SIMD/MMX Instructions without FP Exception

Exception

Re

al

Virtual-8

086

Pr

ot

ected and

Compatibi

lity

64

-bit

Cause of Exception

Invalid Opcode, #UD

X

X

X

X

If CR0.EM[bit 2] = 1.

If ModR/M.mod ≠ 11b

1

NOTES:

1. Applies to MASKMOVQ only.

X

X

X

X

If preceded by a LOCK prefix (F0H)

X

X

X

X

If any corresponding CPUID feature flag is ‘0’

#MF

X

X

X

X

If there is a pending X87 FPU exception

#NM

X

X

X

X

If CR0.TS[bit 3]=1

Stack, SS(0)

X

For an illegal address in the SS segment

X

If a memory address referencing the SS segment is in a non-canonical form

#GP(0)

X

For an illegal memory operand effective address in the CS, DS, ES, FS or GS seg-

ments.

If the destination operand is in a non-writable segment.

2

If the DS, ES, FS, or GS register contains a NULL segment selector.

3

2. Applies to MASKMOVQ and MOVQ (mmreg) only.

3. Applies to MASKMOVQ only.

X

If the memory address is in a non-canonical form.

X

X

If any part of the operand lies outside the effective address space from 0 to FFFFH

#PF(fault-code)

X

X

X

For a page fault

#AC(0)

X

X

X

If alignment checking is enabled and an unaligned memory reference is made while

the current privilege level is 3.

Applicable Instruc-

tions

MASKMOVQ, MOVNTQ, “MOVQ (mmreg)”