22-24 Vol. 3B

ARCHITECTURE COMPATIBILITY

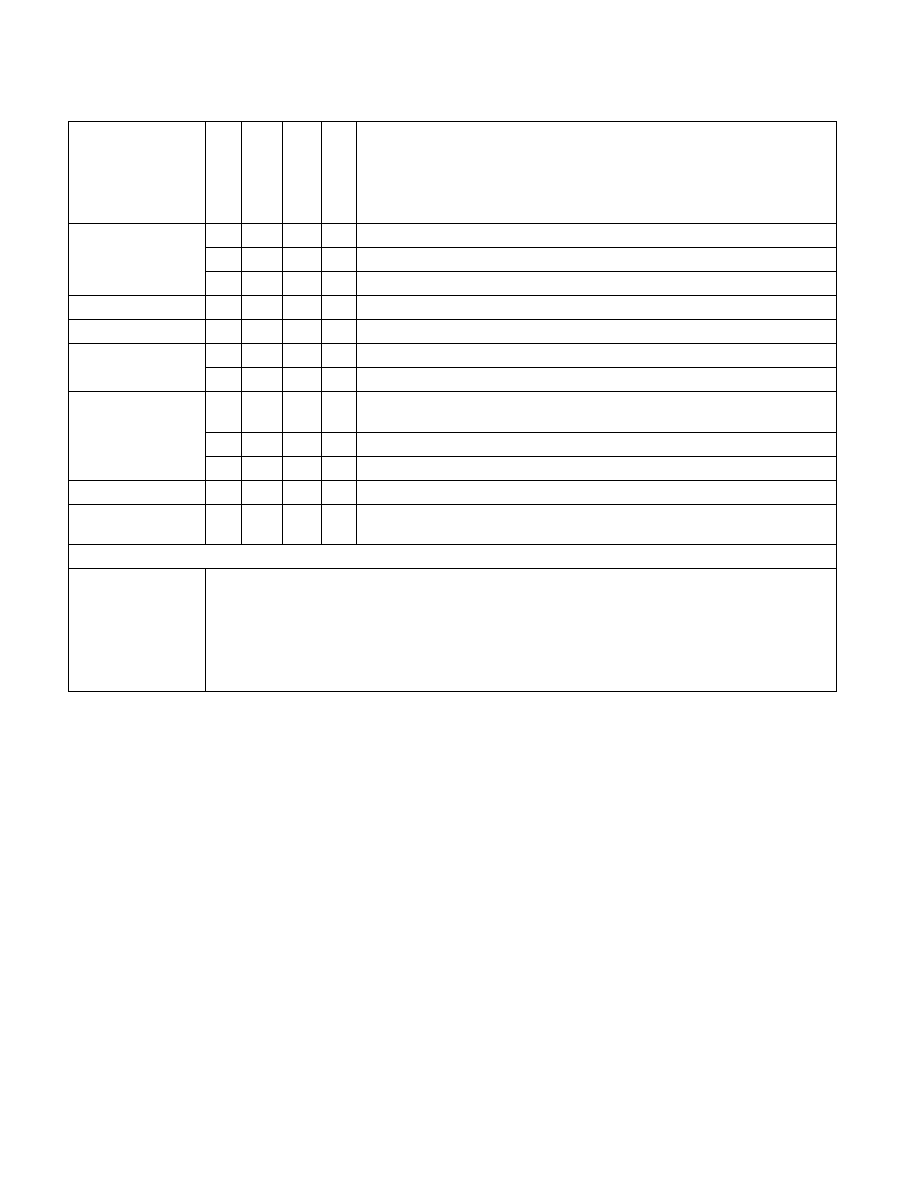

Table 22-7. Exception Conditions for SIMD/MMX Instructions with Memory Reference

Exception

Re

al

Virtual-8

086

Pr

ot

ected and

Compatib

ility

64

-bit

Cause of Exception

Invalid Opcode, #UD

X

X

X

X

If CR0.EM[bit 2] = 1.

X

X

X

X

If preceded by a LOCK prefix (F0H)

X

X

X

X

If any corresponding CPUID feature flag is ‘0’

#MF

X

X

X

X

If there is a pending X87 FPU exception

#NM

X

X

X

X

If CR0.TS[bit 3]=1

Stack, SS(0)

X

For an illegal address in the SS segment

X

If a memory address referencing the SS segment is in a non-canonical form

General Protection,

#GP(0)

X

For an illegal memory operand effective address in the CS, DS, ES, FS or GS seg-

ments.

X

If the memory address is in a non-canonical form.

X

X

If any part of the operand lies outside the effective address space from 0 to FFFFH

#PF(fault-code)

X

X

X

For a page fault

Alignment Check

#AC(0)

X

X

X

If alignment checking is enabled and an unaligned memory reference is made while

the current privilege level is 3.

Applicable Instruc-

tions

PABSB, PABSD, PABSW, PACKSSWB, PACKSSDW, PACKUSWB, PADDB, PADDD, PADDQ, PADDW, PADDSB,

PADDSW, PADDUSB, PADDUSW, PALIGNR, PAND, PANDN, PAVGB, PAVGW, PCMPEQB, PCMPEQD, PCMPEQW,

PCMPGTB, PCMPGTD, PCMPGTW, PHADDD, PHADDW, PHADDSW, PHSUBD, PHSUBW, PHSUBSW, PINSRW,

PMADDUBSW, PMADDWD, PMAXSW, PMAXUB, PMINSW, PMINUB, PMULHRSW, PMULHUW, PMULHW, PMULLW,

PMULUDQ, PSADBW, PSHUFB, PSHUFW, PSIGNB PSIGND PSIGNW, PSLLW, PSLLD, PSLLQ, PSRAD, PSRAW,

PSRLW, PSRLD, PSRLQ, PSUBB, PSUBD, PSUBQ, PSUBW, PSUBSB, PSUBSW, PSUBUSB, PSUBUSW,

PUNPCKHBW, PUNPCKHWD, PUNPCKHDQ, PUNPCKLBW, PUNPCKLWD, PUNPCKLDQ, PXOR